# **Cyclic Combinational Circuits**

Dissertation by

Marc D. Riedel

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Awarded the **Charles H. Wilts Prize** for the Best Doctoral Dissertation in Electrical Engineering.

California Institute of Technology Pasadena, California

June 11, 2004

© 2004

Marc D. Riedel All Rights Reserved

# Acknowledgements

It has been said that the better people are at understanding mathematics the worse they are at understanding human behavior. If so, then perhaps it was a compliment when I declared that my father – Prof. Ivo Rosenberg, a mathematician – would make the worst psychologist in the universe. This characterization aside, my father is the most erudite and principled person that I have known. To him I owe my education, my values, and my passion for research.

To my advisor, Prof. Jehoshua Bruck, I owe my entire research career. Throughout these memorable and rewarding years at Caltech, he has provided unwavering guidance, support and inspiration.

My research was supported in part by a grant from the National Human Genome Research Institute (Grant no. P50 HG02370), and by the Lee Center for Advanced Networking at Caltech.

# Contents

| Acknowledgements i |                       |               |                     |     |  |

|--------------------|-----------------------|---------------|---------------------|-----|--|

| Al                 | bstra                 | $\mathbf{ct}$ |                     | vii |  |

| 1                  | $\operatorname{Intr}$ | oducti        | on                  | 1   |  |

|                    | 1.1                   | A New         | 7 Idea              | 1   |  |

|                    | 1.2                   | Prior V       | Work                | 7   |  |

|                    |                       | 1.2.1         | The Early Era       | 7   |  |

|                    |                       | 1.2.2         | The Later Era       | 10  |  |

|                    | 1.3                   | Overvi        | ew                  | 12  |  |

|                    |                       | 1.3.1         | Theory              | 12  |  |

|                    |                       | 1.3.2         | Practice            | 13  |  |

| <b>2</b>           | Frai                  | neworl        | k                   | 16  |  |

|                    | 2.1                   | Circuit       | t Model             | 16  |  |

|                    |                       | 2.1.1         | Functional Behavior | 18  |  |

|                    |                       | 2.1.2         | Temporal Behavior   | 19  |  |

|                    | 2.2                   | Analys        | sis Framework       | 19  |  |

|                    |                       | 2.2.1         | Ternary Extension   | 20  |  |

|                    |                       | 2.2.2         | Fixed Point         | 22  |  |

|                    |                       | 2.2.3         | Explicit Analysis   | 25  |  |

|                    |                       | 2.2.4         | Complexity          | 30  |  |

|   | 3.1 | Criteria for Optimality                                                                                     |

|---|-----|-------------------------------------------------------------------------------------------------------------|

|   | 3.2 | Fan-in Lower Bound                                                                                          |

|   | 3.3 | Improvement Factor                                                                                          |

|   | 3.4 | Examples                                                                                                    |

|   |     | 3.4.1 Optimality                                                                                            |

|   |     | 3.4.2 Acyclic Lower Bound $\ldots \ldots 40$ |

|   |     | 3.4.3 A Generalization $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 42$           |

|   |     | 3.4.4 Variants $\ldots \ldots 43$     |

|   | 3.5 | A Minimal Cyclic Circuit with Two Gates                                                                     |

|   | 3.6 | Circuits with Multiple Cycles                                                                               |

|   |     | 3.6.1 A Cyclic Circuit with Two Cycles                                                                      |

|   |     | 3.6.2 Analysis in Arbitrary Terms                                                                           |

|   |     | 3.6.3 A Circuit Three-Fifths the Size                                                                       |

|   |     | 3.6.4 A Circuit One-Half the Size                                                                           |

|   | 3.7 | Summary                                                                                                     |

| 4 | Ana | lysis 55                                                                                                    |

|   | 4.1 | Decision Diagrams                                                                                           |

|   | 4.2 | Controlling Values                                                                                          |

|   | 4.3 | Analysis                                                                                                    |

|   |     | 4.3.1 Symbolic Analysis Algorithm                                                                           |

|   |     | 4.3.2 Examples                                                                                              |

| 5 | Syn | thesis 72                                                                                                   |

| 0 | 5.1 | Logic Minimization                                                                                          |

|   | 5.2 | Multi-Level Logic   76                                                                                      |

|   | 5.3 | Substitutional Orderings   78                                                                               |

|   | 5.4 | Branch-and-Bound Algorithms                                                                                 |

|   | 0.4 | 5.4.1 The "Break-Down" Approach                                                                             |

|   |     | 5.4.2 The "Build-Up" Approach                                                                               |

|   |     | $5.4.2$ The bund-op Approach $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\delta \delta$                   |

|   | 5.5 | Example: 7-Segment Decoder                                                                                  |

| 6  | Disc  | cussion                                                | 93  |

|----|-------|--------------------------------------------------------|-----|

|    | 6.1   | High-Level Design                                      | 95  |

|    | 6.2   | Data Structures                                        | 96  |

| A  | open  | dix A: XNF Representation                              | 99  |

| A  | open  | dix B: Synthesis Results                               | 102 |

|    | B-1   | Optimization of Area at the Network Level              | 102 |

|    | B-2   | Optimization of Area at the Gate Level                 | 103 |

|    | B-3   | Joint Optimization of Area and Delay at the Gate Level | 105 |

| Bi | bliog | raphy                                                  | 108 |

# Abstract

A collection of logic gates forms a *combinational* circuit if the outputs can be described as Boolean functions of the current input values only. Optimizing combinational circuitry, for instance, by reducing the number of gates (the area) or by reducing the length of the signal paths (the delay), is an overriding concern in the design of digital integrated circuits.

The accepted wisdom is that combinational circuits must have *acyclic* (i.e., loopfree or feed-forward) topologies. In fact, the idea that "combinational" and "acyclic" are synonymous terms is so thoroughly ingrained that many textbooks provide the latter as a definition of the former. And yet simple examples suggest that this is incorrect. In this dissertation, we advocate the design of *cyclic* combinational circuits (i.e., circuits with loops or feedback paths). We demonstrate that circuits can be optimized effectively for area and for delay by introducing cycles.

On the theoretical front, we discuss lower bounds and we show that certain cyclic circuits are one-half the size of the best possible equivalent acyclic implementations. On the practical front, we describe an efficient approach for *analyzing* cyclic circuits, and we provide a general framework for *synthesizing* such circuits. On trials with industry-accepted benchmark circuits, we obtained significant improvements in area and delay in nearly all cases. Based on these results, we suggest that it is time to re-write the definition: combinational might well mean cyclic.

# Chapter 1 Introduction

New ideas pass through three periods:

- 1. "It can't be done."

- 2. "It probably can be done, but it's not worth doing."

- 3. "I knew it was a good idea all along!"

-Arthur C. Clarke (1917-)

# 1.1 A New Idea

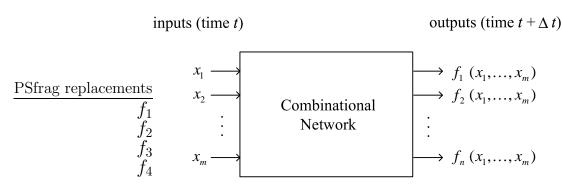

The field of digital circuit design encompasses a broad range of topics, from semiconductor physics to system-level architecture. At the *logic level*, a circuit is viewed as a network of *gates* and *wires* that processes time-varying, discrete-valued signals – most commonly two-valued signals, designated as "0" and "1". Open any textbook on logic design, and you will find digital circuits classified into two types:

- A **combinational** circuit has output values that depend only on the current values applied to the inputs.

- A sequential circuit has output values that depend on the entire sequence of values, past and current, applied to the inputs.

Thus, a sequential circuit can store information, whereas a combinational circuit cannot. Given these *behavioral* definitions, the textbooks describe a *structural* implementation of these types:

- A **combinational** circuit consists of an *acyclic* configuration of logic gates, i.e., it contains only feed-forward paths.

- A sequential circuit consists of a *cyclic* configuration of logic gates and memory elements, i.e., it contains loops or feedback paths.

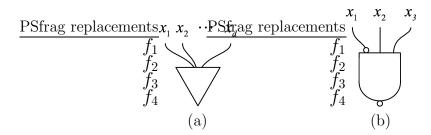

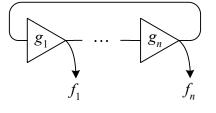

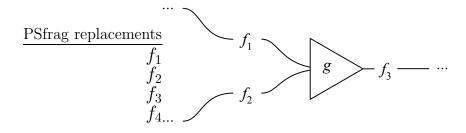

This conforms to intuition. Logic gates are, by definition, feed-forward devices, as illustrated in Figure 1.1. In a feed-forward circuit, such as that shown in Figure 1.2,

Figure 1.1: A logic gate is a feed-forward device.

the input values propagate forward and determine the values of the outputs. The outcome can be asserted regardless of the prior values of the wires, and so independently of the past sequence of inputs. The circuit is clearly combinational.

Figure 1.2: A feed-forward circuit behaves combinationally.

In a circuit with feedback, the behavior is less transparent. A common approach is to characterize the output values and the *next* state in terms of the input values and the *current* state. The current state, in turn, depends on the prior sequence of inputs (starting from some known initial state). As an example, the cyclic circuit shown

| $s \sim$              | s(t) | r(t) | q(t) | q(t+1)  |

|-----------------------|------|------|------|---------|

|                       | 0    | 0    | 0    | 0       |

| NOR o q               | 0    | 0    | 1    | 1       |

| PSfrag replacements ( | 0    | 1    | 0    | 1       |

| $f_1$                 | 0    | 1    | 1    | 1       |

| $f_2$                 | 1    | 0    | 0    | 0       |

| f NOR                 | 1    | 0    | 1    | 0       |

| $J_3 f_{4r}$          | 1    | 1    | 0    | $\perp$ |

|                       | 1    | 1    | 1    | $\perp$ |

in Figure 1.3 implements a one-bit memory element, called a *latch*. This circuit is clearly sequential.

Figure 1.3: A circuit with feedback. With inputs s(t) and r(t), and current state q(t), the next state is q(t + 1). Here  $\perp$  indicates an indeterminate value.

Although counter-intuitive, could a combinational circuit be designed *with* feed-back paths?

#### "It can't be done."

One might argue that with feedback, we cannot determine the output values without knowing the current state, and so the circuit must be sequential. This view is illustrated in Figure 1.4.

Figure 1.4: A circuit with feedback. How can we determine the output f without knowing the value of y in a feedback path?

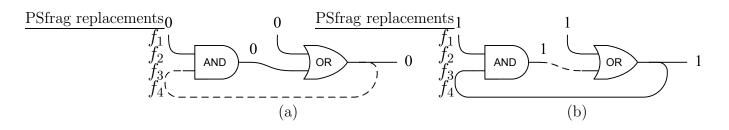

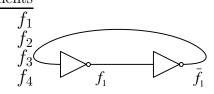

This specious argument can easily be put to rest with the circuit in Figure 1.5. It consists of an AND gate and an OR gate connected in a cycle, both with input x.

Figure 1.5: A (useless) cyclic combinational circuit.

Recall that the output of an AND gate is 0 iff either input is 0; the output of an OR gate is 1 iff either input is 1. Consider the two possible values of x. On the one hand, if x = 0 then the output of the AND gate is fixed at 0; the input from the OR gate has no influence, as shown in Figure 1.6 (a). On the other hand, if x = 1 then the output of the OR gate is fixed at 1; the input from the AND gate has no influence, as shown in Figure 1.6 (b). Although useless, this circuit is cyclic and combinational. The value of the output f is determined by the current input value x (actually f = x) regardless of the prior state and independently of all timing assumptions.

Figure 1.6: The circuit of Figure 1.5 with (a) x = 0, and (b) x = 1.

#### "It probably can be done, but it's not worth doing."

Although conceptually possible, one might argue that there is *no point* in designing combinational circuits with feedback. Why should one incorporate a feedback path in the computation of the output values? By definition the values fed back depend upon the prior state of the circuit, which we want to *ignore* in a combinational design.

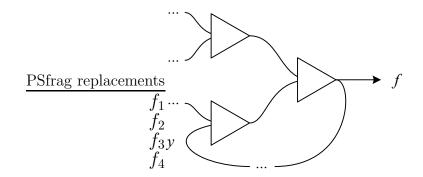

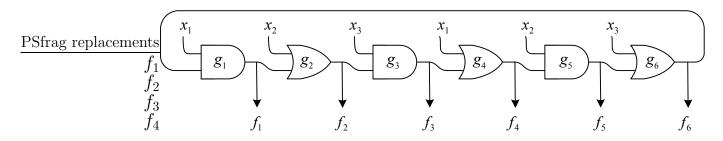

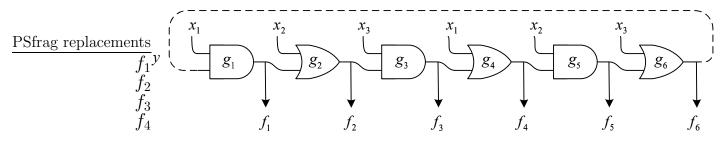

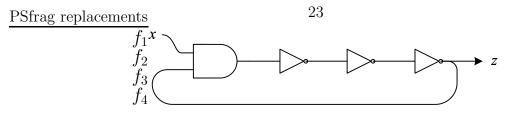

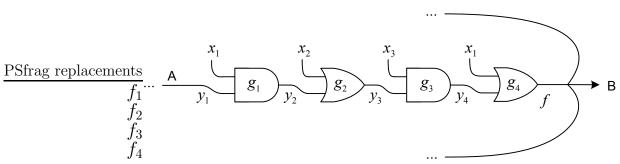

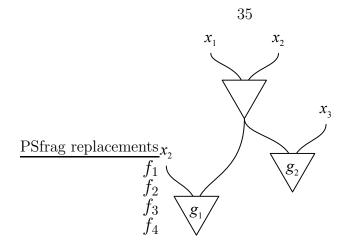

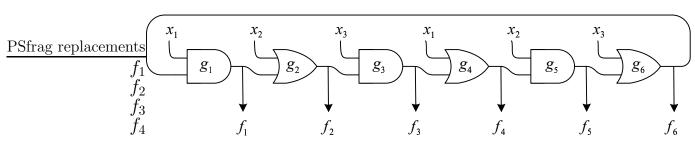

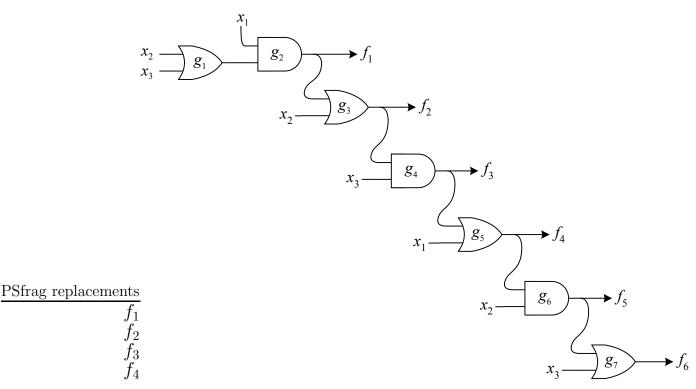

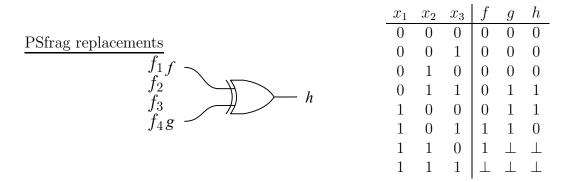

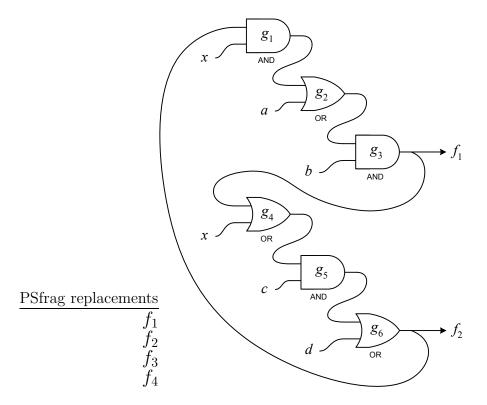

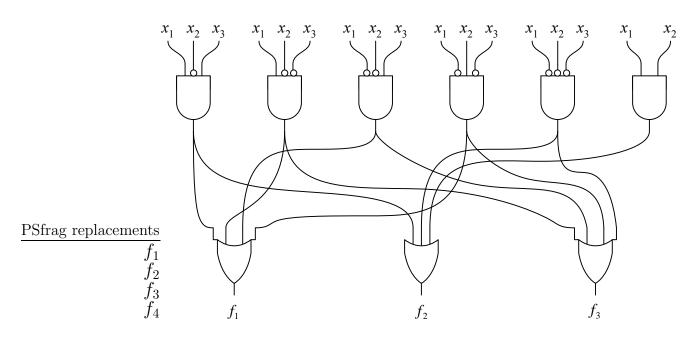

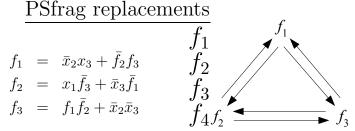

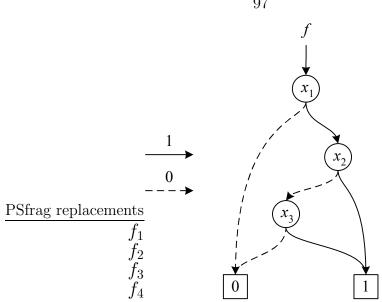

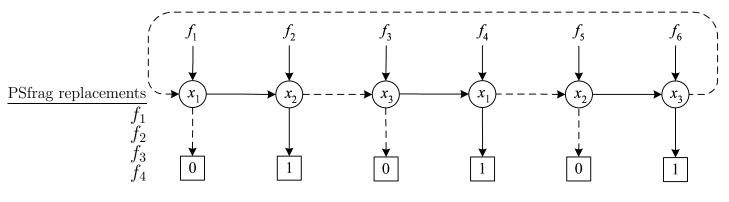

A convincing example suggesting otherwise is shown in Figure 1.7. It consists of six alternating AND and OR gates, with inputs  $x_1, x_2, x_3$  repeated. To show that the circuit is combinational, we label the feedback path with an unknown value y, as

Figure 1.7: A cyclic combinational circuit due to Rivest [35].

shown in Figure 1.8. We compute

$$f_{1} = x_{1}y$$

$$f_{2} = x_{2} + f_{1} = x_{2} + x_{1}y$$

$$f_{3} = x_{3}f_{2} = x_{3}(x_{2} + x_{1}y)$$

$$f_{4} = x_{1} + f_{3} = x_{1} + x_{3}(x_{2} + x_{1}y) = x_{1} + x_{2}x_{3}$$

$$f_{5} = x_{2}f_{4} = x_{2}(x_{1} + x_{2}x_{3}) = x_{2}(x_{1} + x_{3})$$

$$f_{6} = x_{3} + f_{5} = x_{3} + x_{2}(x_{1} + x_{3}) = x_{3} + x_{1}x_{2}.$$

(Here addition represents OR and multiplication represents AND.) We see that  $f_4$ , and consequently  $f_5$  and  $f_6$ , do not depend upon the unknown value. Thus, we compute

$$f_1 = x_1 f_6 = x_1 (x_3 + x_1 x_2) = x_1 (x_2 + x_3)$$

$$f_2 = x_2 + f_1 = x_2 + x_1 (x_2 + x_3) = x_2 + x_1 x_3$$

$$f_3 = x_3 f_2 = x_3 (x_2 + x_1 x_3) = x_3 (x_1 + x_2).$$

Each output depends on the current input values, not on the prior values, and so the circuit is combinational.

Figure 1.8: Analyzing the circuit of Figure 1.7.

#### PSfrag replacements

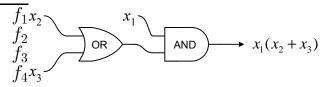

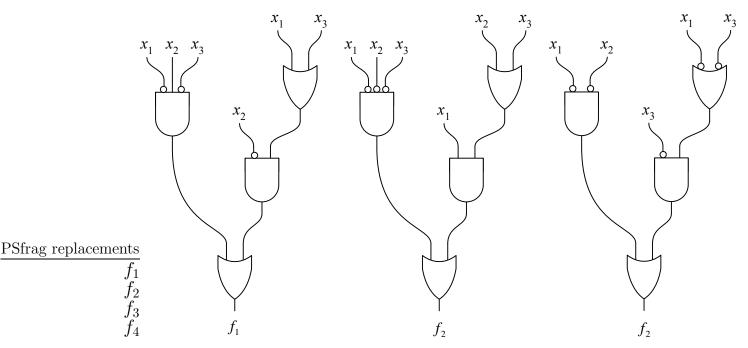

Figure 1.9: With fan-in two gates, two gates are needed to compute  $x_1(x_2 + x_3)$ .

Unlike the circuit in Figure 1.5, this one computes something useful. The six output functions are distinct, and each depends on all three input variables. Moreover, we can show that this cyclic circuit has *fewer* gates than any equivalent acyclic circuit. To see this, note that any acyclic configuration contains at least one gate producing an output function that does not depend on the output of any other gate producing an output function. (If this were not the case, then every output gate would depend upon another and so the circuit would be cyclic.) With fan-in two gates, it takes two gates to compute any one of the six functions by itself. This is illustrated in Figure 1.9. We conclude that an acyclic implementation of the six functions requires seven gates, compared to the six in the cyclic circuit.

#### "I knew it was a good idea all along!"

The circuit in Figure 1.7 was presented by Rivest in 1977, in a paper less than a page long [35]. His work on the topic, as well as that of a few others in the 1960s, seems to have gone largely unnoticed by theoreticians and practitioners alike. And yet his example hints at a fundamental misconception in the field, namely that "combinational" and "acyclic" are synonymous terms. In this dissertation, we demonstrate not only that it is feasible to design combinational circuits with cyclic topologies, but it is generally advantageous to do so.

## 1.2 Prior Work

#### 1.2.1 The Early Era

Figure 1.10: A contact relay.

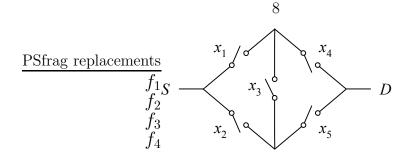

Switching circuits were the subject of seminal papers by Claude Shannon: the analysis of such circuits in 1938 [39] and the synthesis of such circuits in 1949 [40]. The circuits of Shannon's day often had cyclic topologies. Since relays are directionless, cycles do not pose any problem. Consider the *bridge* circuit shown in Figure 1.11. The logical function implemented between points S and D is

$$f(x_1, x_2, x_3, x_4, x_5) = x_1 x_4 + x_1 x_3 x_5 + x_2 x_5 + x_2 x_3 x_4.$$

It may be shown this circuit has fewer switches than is possible with an acyclic topology.

It was accepted that cycles were an important feature in the design of switching circuits. In 1953, Shannon described a cyclic switching circuit with 18 contacts that computes all 16 Boolean functions of two inputs, and he proved that this circuit is optimal [41].

In his Ph.D. dissertation in 1960, Short applied an abstract graphical model to the study of switching circuits [45]. Implicitly, his model imposes a direction on the

Figure 1.11: A switching circuit with a cyclic topology.

switching elements. It is equivalent to a form of binary decision diagram now known as a *zero-suppressed* decision diagram [30]. In this context, Short argued that cyclic designs are necessary for the minimal forms.

In recent years, binary decision diagrams have come to the fore as perhaps the most successful data structure for representing Boolean functions [7]. Short's work suggests that feedback might be useful in optimizing binary decision diagrams, a topic of future research that we return to in Chapter 6.

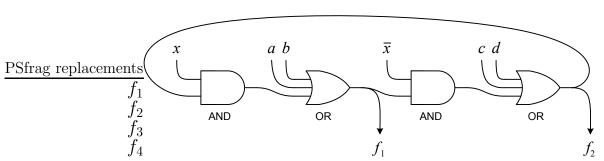

In the 1960's, as the research community was shifting its focus to the now-familiar model of of directed logic gates (AND, OR, NOT, etc.), researchers naturally pondered the implication of cyclic designs. In 1963, McCaw presented a thesis for his Engineer's Degree titled "Loops in Directed Combinational Switching Networks" [26]. He begins with an example, the cyclic circuit shown in Figure 1.12 consisting of two AND gates and two OR gates, with five inputs and two outputs. His argument for combinationality is in the same vein as that given above for Rivest's circuit:

$$f_1 = a + b + x(c + d + \bar{x}f_1) = a + b + x(c + d)$$

$$f_2 = c + d + \bar{x}(a + b + xf_2) = c + d + \bar{x}(a + b)$$

As with Rivest's circuit, McCaw argues that his circuit has fewer AND/OR gates than is possible with an acyclic circuit implementing the same functions. In his thesis, he grapples with the different implications of cyclic topologies for circuits with logic gates vs. undirected switching elements. As an example, he transforms a switching circuit in Short's dissertation, consisting of 7 switching elements, into a cyclic logic circuit consisting of 16 AND/OR gates.

Figure 1.12: A cyclic combinational circuit due to McCaw.

In 1970, Kautz (Short's Ph.D. advisor at Stanford) presented a short paper on the topic of feedback in circuits with logic gates [17]. He described a cyclic circuit consisting of 6 fan-in two NOR gates with three inputs and three outputs. Although plausible, his circuit is not combinational according to the rigorous model that we propose. (It assumes that all wires have definite Boolean values at the outset.)

In 1971, Huffman discussed feedback in linear threshold networks. He claimed that an arbitrarily large number of input variables can be complemented in a network containing a single NOT element, provided that feedback is used [15]. This improved upon an earlier result by Markov, demonstrating that k NOT elements suffice to generate the complements of  $2^k - 1$  variables [25]. As with Kautz's example, Huffman's is not combinational in the sense that we understand it. Still, in an insightful commentary on his and Kautz's work, he hinted at the possible implications,

"At this time, these [cyclic] examples are isolated ones. They do, however, provide tantalizing glimpses into an imaginable area of future research."

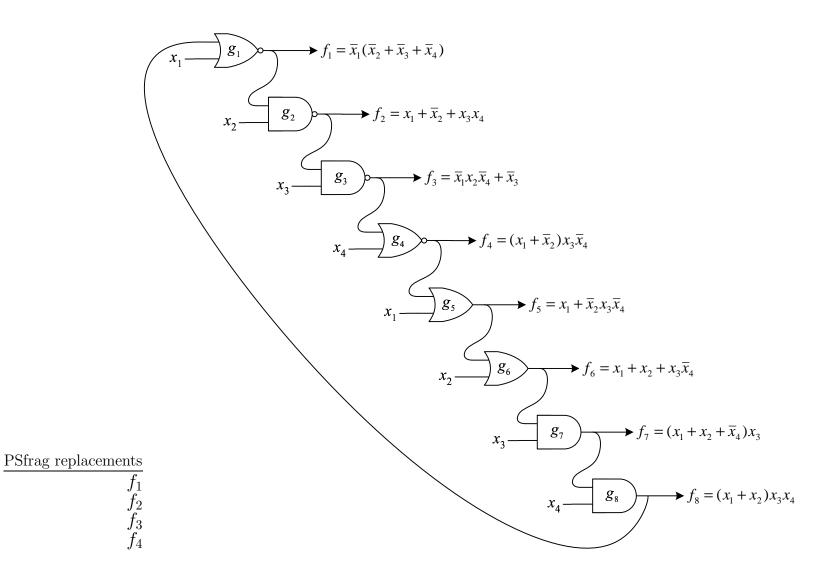

In 1977, Rivest presented a general version of the circuit in Figure 1.7, as well as the argument for its optimality given above [35]. For any odd integer n greater than 1, the general circuit consists of n fan-in two AND gates alternating with n fan-in two OR gates, with input variables  $x_1, \ldots, x_n$  arranged as in Figure 1.7. It produces 2n distinct output functions, each of which depends on all n input variables. He proved that any acyclic circuit implementing the same 2n output functions requires at least 3n - 2 fan-in two gates. Thus, asymptotically, his cyclic implementation is at most two-thirds the size of the best possible acyclic implementation. In Section 3, we analyze Rivest's construction, present variants and extensions, and generalize the argument of optimality

#### 1.2.2 The Later Era

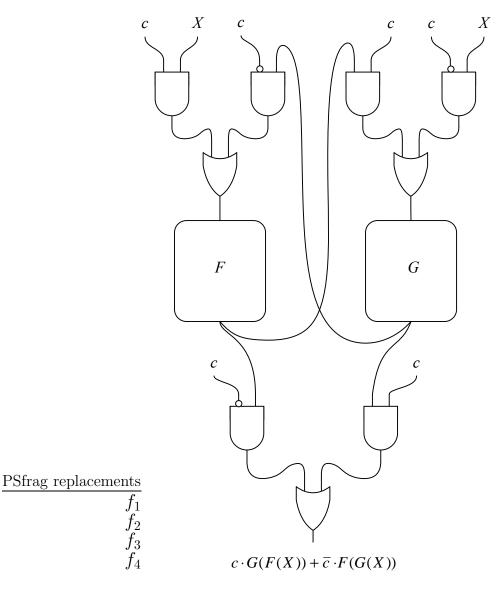

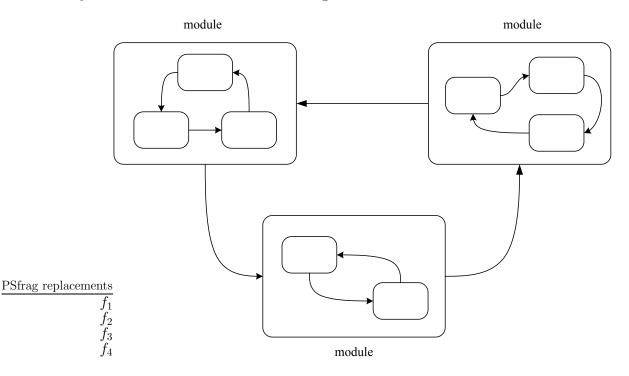

More recently, practitioners observed that cycles sometimes occur in combinational circuits synthesized from high-level descriptions. In such examples, feedback either is inadvertent or else is carefully contrived. For instance, occasionally it is introduced during resource-sharing optimizations at the level of functional units [47]. In these circuits, there is explicit "control" circuitry governing the interaction between "functional" units.

Consider the example in Figure 1.13. Here we have an input word X (that is, a bundle of wires carrying several bits of information) and a control input c. There are two functional units, F and G, each of which performs a word-wise operation. If c is 1, then the circuit computes

while if it is 0, it computes

F(G(X)).

Suppose that  $X = (x_1, \ldots, x_n)$  is an *n*-bit word, representing the integer

$$x_1 + 2x_2 + \dots + 2^{n-1}x_n$$

.

Here F(X) might be an exponentiation

$$F(X) = 2^X \mod 2^n,$$

and G(X) might be a left-shift (division by 2),

$$G(X) = \left\lfloor \frac{X}{2} \right\rfloor.$$

The circuit either performs a left-shift followed by an exponentiation, or an exponen-

tiation followed by a left-shift.

Figure 1.13: Functional units connected in a cyclic topology.

Although clearly promising, the idea of cyclic designs at the level of functional units has not been pursued, due to a lack of support in integrated circuit design packages. Indeed, nearly all logic synthesis and verification tools balk when given designs with cycles. Methods were proposed for analyzing such designs [12], [24], [42]. Nevertheless, the accepted strategy is simply to disallow cycles among functional units in the high-level phases.

### 1.3 Overview

In the realm of digital circuits, researchers seems to fall into two camps. On the one hand, there are the theoreticians, working in the field of circuit complexity. They are preoccupied with *classifying* and *characterizing* problems in general terms. They discuss the relationships among complexity classes, and prove bounds on the size of circuits. On the other hand, there are the practitioners, working in the field of electronic design automation. They strive to obtain the best circuits that they can, given the computational resources at their disposal. However, they rarely speak of *optimal* designs. The true optimum according to any criteria – be it area, delay, power – is generally unknowable to them.

#### 1.3.1 Theory

In the first half of this dissertation, we wear the theoretician's mantle. In Chapter 2 we describe our circuit model, and present a framework for analysis. In Chapter 3, we present theoretical justification for the claim that the optimal form of some circuits requires cyclic topologies. We exhibit families of cyclic circuits that are optimal in the number of gates, and we prove lower bounds on the size of equivalent acyclic circuits.

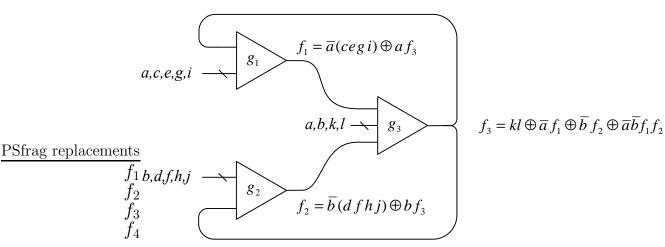

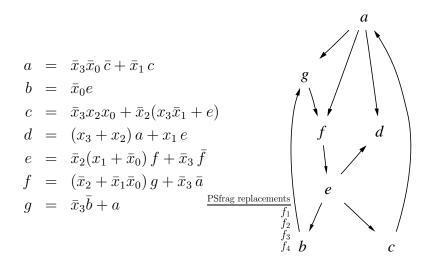

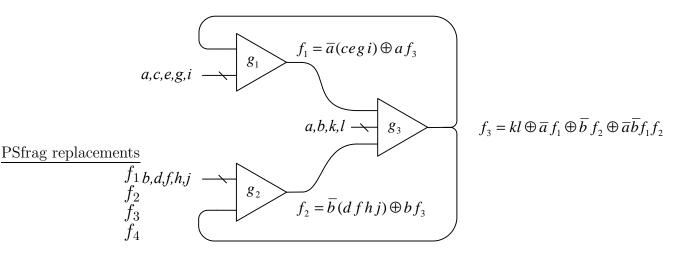

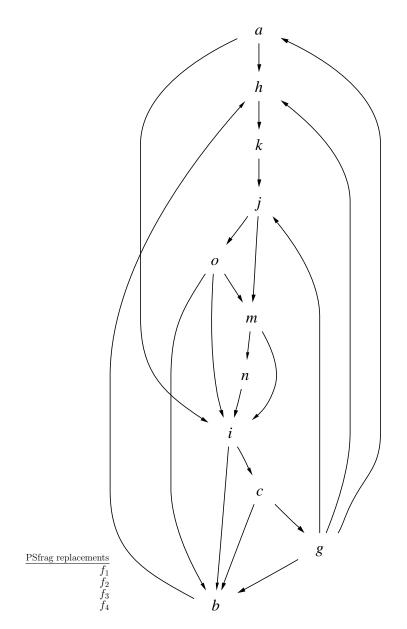

For instance, the cyclic circuit in Figure 1.14 consists of three "complex" gates, each with fan-in 6. We show that this circuit implements three distinct functions,  $f_1$ ,  $f_2$  and  $f_3$ , each depending on all 12 variables  $a, \ldots, l$ . We then argue that an acyclic circuit implementing the same functions requires at least five fan-in 6 gates.

Our lower bound is based on a simple fan-in argument: in order to compute a function that depends on a certain number of variables using gates with a certain fan-in, we require a tree of at least a certain size. This is perhaps the *weakest* lower bound than one can conceive of on a circuit's size. This suggests that feedback may be *more* powerful than we can show.

Our most notable construction is a family of cyclic circuits that have asymptotically at most one-half as many gates as equivalent acyclic circuits. We show that this is largest gap that we can prove using the the fan-in lower bound technique.

Figure 1.14: Cyclic circuit with inputs  $a, \ldots, l$  and outputs  $f_1, f_2, f_3$ . ( $\oplus$  represents XOR.)

#### 1.3.2 Practice

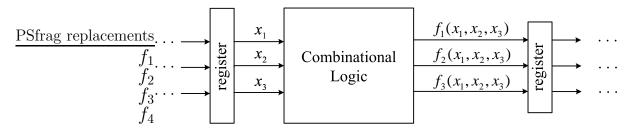

In the second half of the dissertation, we wear the practitioner's mantle. In Chapter 5 we describe a general methodology for synthesizing cyclic combinational circuits, and compare our results to those produced by state-of-the art logic synthesis tools.

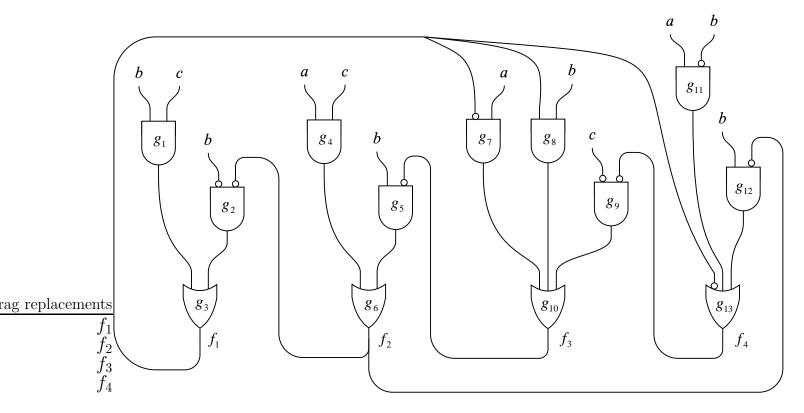

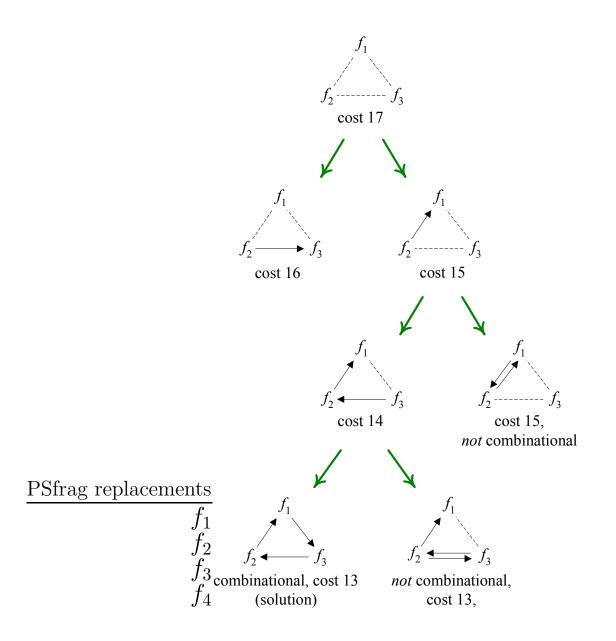

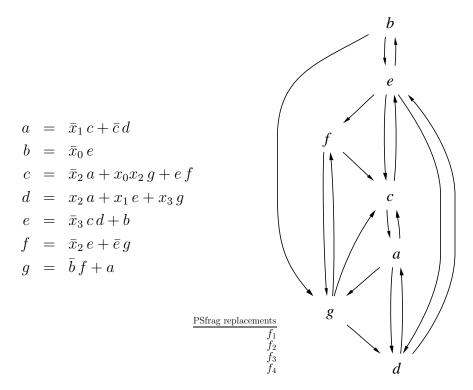

Consider the example shown in Figure 1.15, ubiquitous in introductory logic design courses: a 7-segment display decoder. The inputs are four bits,  $x_0, x_1, x_2, x_3$ , specifying a number from 0 to 9. The outputs are 7 bits, a, b, c, d, e, f, g, specifying which segments to light up in a display – such as that of a digital alarm clock – to form the image of this number.

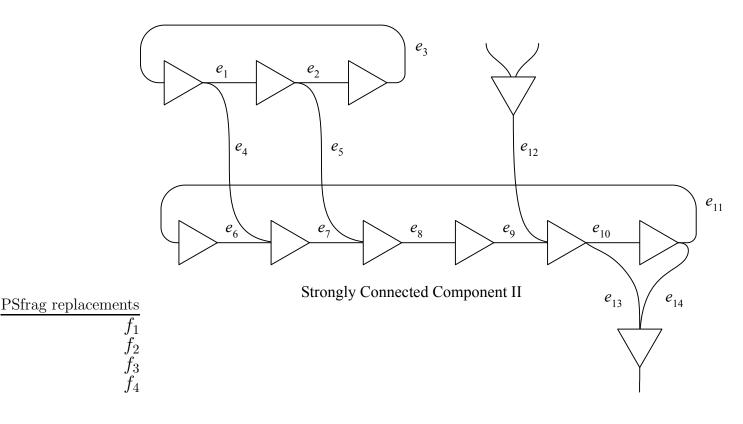

With our synthesis methodology, we arrive at the network shown in Figure 1.16, with the ordering illustrated. This network translates into a cyclic circuit with 27 fan-in two gates. In contrast, standard synthesis techniques produce an acyclic circuit with 32 fan-in two gates.

Note that the network in Figure 1.16 contains cyclic dependencies; in fact, all the functions except d form a strongly connected component. How can we establish that this network computes what it is supposed to, namely the output functions for the 7-segment decoder? We refer to this task as *functional analysis*. Given an upper bound on the time that it takes each gate to compute a value – the *gate delay* – how can we establish an upper bound on the time that it takes for the circuit to compute the

|       | inp   | outs  |       |       |   |   | out | put | $\mathbf{s}$ |         |      |                    |   |   |

|-------|-------|-------|-------|-------|---|---|-----|-----|--------------|---------|------|--------------------|---|---|

| $x_3$ | $x_2$ | $x_1$ | $x_0$ | Digit | a | b | с   | d   | е            | f       | g    | _                  |   |   |

| 0     | 0     | 0     | 0     | 0     | 1 | 1 | 1   | 0   | 1            | 1       | 1    |                    | С |   |

| 0     | 0     | 0     | 1     | 1     | 0 | 0 | 0   | 0   | 0            | 1       | 1    |                    |   | λ |

| 0     | 0     | 1     | 0     | 2     | 0 | 1 | 1   | 1p  | Sfra         | $1^{1}$ | ebla | $a_{\rm cements}a$ | 7 | f |

| 0     | 0     | 1     | 1     | 3     | 0 | 0 | 1   | 1   | 1            | 1       | 1    | $f_1$              | d |   |

| 0     | 1     | 0     | 0     | 4     | 1 | 0 | 0   | 1   | 0            | 1       | 1    | $\int_{0}^{1}$     |   |   |

| 0     | 1     | 0     | 1     | 5     | 1 | 0 | 1   | 1   | 1            | 0       | 1    | $J_2 b f_2$        |   | g |

| 0     | 1     | 1     | 0     | 6     | 1 | 1 | 0   | 1   | 1            | 0       | 1    | $J_{4}^{J_{3}}$    |   | y |

| 0     | 1     | 1     | 1     | 7     | 0 | 0 | 1   | 0   | 0            | 1       | 1    | J4                 | е |   |

| 1     | 0     | 0     | 0     | 8     | 1 | 1 | 1   | 1   | 1            | 1       | 1    |                    |   |   |

| 1     | 0     | 0     | 1     | 9     | 1 | 0 | 1   | 1   | 0            | 1       | 1    |                    |   |   |

Figure 1.15: 7-Segment Display Decoder.

values of the functions – the *circuit delay*? We refer to this task as *timing analysis*.

Khrapchenko was the first to recognize that depth and delay in a circuit are not equivalent concepts [18]. There may exist *false paths*, that is to say, topological paths that are never sensitized. So-called "exact" algorithms for timing analysis consider the presence of false paths; these provide the requisite tool for the analysis of cyclic circuits. For a cyclic circuit, we can say that it is combinational if all cycles are false; the sensitized paths in the circuit never bite their own tail to form true cycles.

Our synthesis program can routinely tackle designs with, say 50 inputs and 30 outputs. For circuits of this size, a exhaustive approach to analysis – that is to say, checking every input assignment – is not feasible: with n variables there would be  $2^n$  input combinations. In Chapter 4 we describe efficient algorithms for analysis based on *symbolic* techniques, using flexible data structures called *binary decision diagrams*. Our analysis considers topological aspects of the design, for instance sub-dividing the problem into strongly connected components.

Our synthesis strategy is to introduce feedback in the re-restructuring and minimization phases. A branch-and-bound search is performed, with analysis used to validated and rank potential solutions. Although general, our methodology is of immediate practical interest. For instance, we optimized the area of the ALU Decoder of a 8051 microprocessor design by 20%. In trials with benchmark circuits, nearly all

Figure 1.16: A cyclic network for the example in Figure 1.15.

were optimized significantly, with improvements of up to 30% in the area and up to 25% in the delay.

Theoreticians may dismiss optimizations of this sort as inconsequential:

"Saving a few gates in the design of a 7-segment decoder doesn't prove anything".

Practitioners may dismiss the theoretical results as contrived:

"Asymptotic bounds don't help me one bit in designing real circuits.".

However, taken together our results should convince both camps. It is time to re-write the definition: in both theory and practice, combinational might well mean cyclic.

# Chapter 2 Framework

Make everything as simple as possible without making anything too simple.Albert Einstein (1879–1955)

The concepts discussed in this dissertation are not tied to any particular physical model or computing substrate. For the core ideas in Chapter 4 and Chapter 5, the exposition is at a *symbolic* level, that is to say, in terms of Boolean expressions. However, we first postulate an underlying *structural* model, consisting of *gates* and *wires*, and discuss analysis in an explicit sense – in terms of signal values.

# 2.1 Circuit Model

We work with digital abstraction of 0's and 1's. Nevertheless, our model recognizes that the underlying signals are, in fact, analog: each signal is a continuous realvalued function of time s(t), corresponding to a voltage level. For analysis, we adopt a *ternary* framework, extending the set of *Boolean* values  $\mathbb{B} = \{0, 1\}$  to the set of ternary values  $\mathbb{T} = \{0, 1, \bot\}$ . The logical value of an analog signal is obtained by the mapping

$$\operatorname{logical}[s(t)] = \begin{cases} 0 & \text{if } s(t) < V_{\operatorname{low}} \\ 1 & \text{if } s(t) > V_{\operatorname{high}} \\ \bot & \text{otherwise,} \end{cases}$$

where  $V_{\text{low}}$  and  $V_{\text{high}}$  are real values demarcating the range corresponding to Boolean 0 and Boolean 1, respectively. Clearly,  $V_{\text{high}}$  must be strictly greater than  $V_{\text{low}}$ . The third value,  $\perp$ , indicates that the signal is ambiguous. For the purposes of analysis,  $\perp$  is used in a broader sense: it denotes a signal value that is *unknown*. This signal may be Boolean 0, Boolean 1, or some ambiguous value – we simply do not know.

The idea of three-valued logic for circuit analysis is well established. It was originally proposed for the analysis of *hazards* in combinational logic [13], [50]. Bryant popularized its use for verification [8], and it has been widely adopted for the analysis of asynchronous circuits [9]. For a theoretical treatment, see [29].

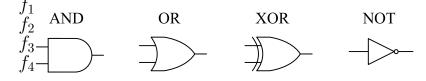

A circuit consists of **gates** connected by **wires**. Each gate has one or more inputs and a single output. The symbols for common gates are shown in Figure 2.1. A bubble is used to indicate that an input or output is negated, as illustrated in Figure 2.2. PSfrag replacements

Figure 2.1: Symbols for different types of gates. PSfrag replacements  $\begin{array}{c} f_1 \\ f_2 \\ f_3 \\ f_4 y \end{array} \xrightarrow{f_1 \\ f_2 \\ f_3 \\ f_4 y \end{array} \xrightarrow{z}$

Figure 2.2: Bubbles on the inputs or the output of a gate indicate negation. Here z = NOT(OR(NOT(x), y)).

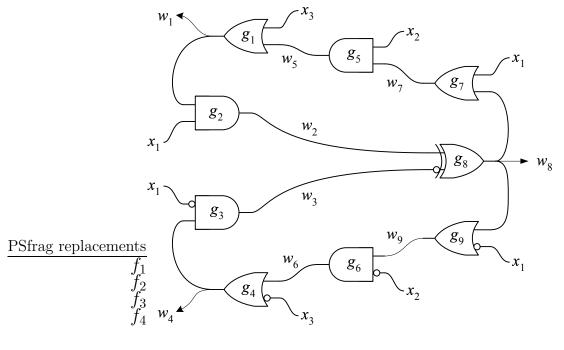

An example of a circuit is shown in Figure 2.3. Even though a wire may split in our diagrams, as is the case with wire  $w_8$  in Figure 2.3, conceptually there is a single instance of it.

• The circuit accepts signals  $x_1, \ldots, x_m$ , ranging over  $\{0, 1\}$ , called the **primary** inputs. Each primary input is fed into one or more gate inputs. Even though the symbol for a primary input may appear in several places, as is the case with  $x_1, x_2$  and  $x_3$  in Figure 2.3, conceptually there is a single instance of it.

- The gates in the circuit produce internal signals,  $w_1, \ldots, w_n$  ranging over  $\{0, 1, \bot\}$ .

- A subset of the set of internal signals is designated as the set of **primary outputs**.

input signals:  $x_1, x_2, x_3$ internal signals:  $w_1, \ldots, w_9$ output signals:  $w_1, w_4, w_8$ gates:  $g_1, \ldots, g_9$

Figure 2.3: An example of a circuit, consisting of gates and wires.

### 2.1.1 Functional Behavior

In the digital realm, a gate implements a Boolean function, i.e., a mapping from Boolean inputs to a Boolean output value,

$$g: \{0,1\}^k \to \{0,1\}.$$

The set of inputs to a gate are called its **fan-in** set. When we say a "fan-in k" gate, we mean a gate with fan-in set of cardinality k. The set of gates that are attached to a gate output are called its **fan-out** set. The truth tables for fan-in two AND, OR and XOR gates, as well as a fan-in one NOT gate, are shown Figure 2.4.

| x | y | AND(x, y) | OR(x, y) | XOR(x, y) |

|---|---|-----------|----------|-----------|

| 0 | 0 | 0         | 0        | 0         |

| 0 | 1 | 0         | 1        | 1         |

| 1 | 0 | 0         | 1        | 1         |

| 1 | 1 | 1         | 1        | 0         |

| x | NOT(x) |

|---|--------|

| 0 | 1      |

| 1 | 0      |

Figure 2.4: Truth table for common gates.

#### 2.1.2 Temporal Behavior

We characterize the temporal behavior of a gate by a single parameter, a bound on its delay  $t_d$ .

For a gate characterized by a mapping g, if the inputs assume the values  $y_1(t), \ldots, y_k(t)$  at time t, and subsequently do not change, then the output assumes the value  $g[y_1(t), \ldots, y_k(t)]$  at time no later than  $t + t_d$ , and does not change.

Further, we assume that the wires have zero propagation delay. More realistic models for timing analysis can readily be incorporated within our framework; we neglect such details here in order to focus on the conceptual aspects.

## 2.2 Analysis Framework

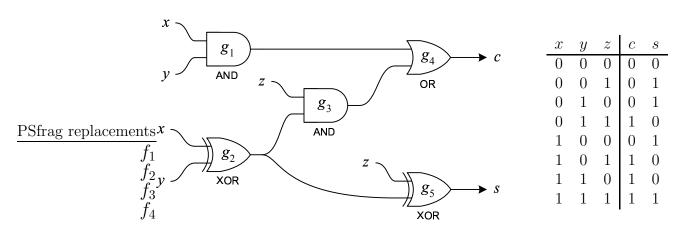

Our analysis characterizes the functional behavior of circuits according to the socalled "floating-mode" assumption [9], [49]: at the outset of each interval, all wires in a circuit are assumed to have unknown or possibly undefined values ( $\perp$ ). We apply definite values to the inputs, and track the propagation of signal values. Analysis of an *acyclic* circuit is transparent. We first evaluate the gates connected only to primary inputs, and then gates connected to these and primary inputs, and so on, until we have evaluated all gates. For instance, in the circuit of Figure 1.2 in the Introduction, we first evaluate  $g_1$  and  $g_2$ , then  $g_3$ , then  $g_4$  and  $g_5$ . At each step, we only evaluate a gate when all of its input signals are known. The previous values of the internal signals do not enter into play.

In a cyclic circuit, there are one or more strongly connected components. Recall that in a directed graph G, a strongly connected component is an induced subgraph  $S \subseteq G$  such that

- there exists a directed path between every pair of nodes in S;

- for every node s in S and every node n outside of S, if there exists a path from s to n (from n to s) then there is no path from n to s (from s to n, respectively).

We analyze each strongly connected component separately.

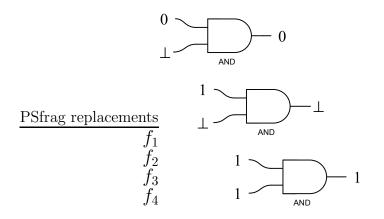

At the outset, with only the primary inputs fixed at definite values, each gate in a strongly connected component has some unknown/undefined inputs (valued  $\perp$ ). Nevertheless, for each such gate we can ask: is there sufficient information to conclude that the gate output is 0 or 1, in spite of the  $\perp$  values? If yes, we assign this value as the output; otherwise, the value  $\perp$  persists. For instance, with an AND gate, if the inputs include a 0, then the output is 0, regardless of other  $\perp$  inputs. If the inputs consist of 1 and  $\perp$  values, then the output is  $\perp$ . Only if all the inputs are 1 is the output 1. This is illustrated in Figure 2.5. Input values that determine the gate output are called *controlling*.

#### 2.2.1 Ternary Extension

For the set  $\{0, 1, \bot\}$ , we define a **partial ordering**

$$\perp \sqsubseteq 0$$

and  $\perp \sqsubseteq 1$ ,

Figure 2.5: An AND gate with 0, 1, and  $\perp$  inputs.

with 0 and 1 not comparable. For vectors  $Y = (y_1, \ldots, y_n)$  and  $Z = (z_1, \ldots, z_n)$ , we define the ordering coordinate-wise:

$$Y \sqsubseteq Z$$

if  $y_i \sqsubseteq z_i$  for all  $i = 1, \ldots, n$ .

For instance, if  $Y = (\perp, 1, \perp, 0)$ , and Z = (1, 1, 1, 0) then  $Y \sqsubseteq Z$ . However, if  $Y = (\perp, 1, \perp, 0)$  and  $Z = (1, 1, 1, \perp)$  then Y and Z are not comparable.

We define the **partial join**  $V = (v_1, \ldots, v_n) = Y \sqcup Z$  as:

$$v_{i} = \begin{cases} a & \text{if } y_{i} = z_{i} = a \text{ for some } a \in \{0, 1\}, \\ b & \text{if } \{y_{i}, z_{i}\} = \{b, \bot\} \text{ for some } b \in \{0, 1\}, \\ \bot & \text{else.} \end{cases}$$

for all i = 1, ..., n. For instance, if  $Y = (\bot, 1, \bot, 0)$ , and  $Z = (1, 1, 1, \bot)$  then  $Y \sqcup Z = (1, 1, 1, 0)$ .

Within the ternary framework, a gate performs a mapping from ternary values to ternary values,

$$g': \{0, 1, \bot\}^k \to \{0, 1, \bot\}.$$

We call this mapping the *ternary extension* of g. Given a Boolean mapping g, the **ternary extension** g' is defined as follows. For a vector of ternary values  $Y \in$

$\{0,1,\bot\}^k,$

$$g\prime(Y) = \begin{cases} 0 & \text{if } g(Z) = 0 \text{ for each } Z \in \{0,1\}^k, \text{ where } Y \sqsubseteq Z, \\ 1 & \text{if } g(Z) = 1 \text{ for each } Z \in \{0,1\}^k, \text{ where } Y \sqsubseteq Z, \\ \bot & \text{else.} \end{cases}$$

A similar definition of the ternary extension is found in [9]. The truth-tables for the ternary extensions of fan-in two AND, OR and XOR gates, as well as a fan-in one NOT gate, are shown in Figure 2.6.

| x       | y       | AND(x, y) | OR(x, y) | XOR(x, y) |

|---------|---------|-----------|----------|-----------|

| 0       | 0       | 0         | 0        | 0         |

| 0       | 1       | 0         | 1        | 1         |

| 0       | $\perp$ | 0         | $\perp$  | $\perp$   |

| 1       | 0       | 0         | 1        | 1         |

| 1       | 1       | 1         | 1        | 0         |

| 1       | $\perp$ | $\perp$   | 1        | $\perp$   |

| $\perp$ | 0       | 0         | $\perp$  | $\perp$   |

| $\perp$ | 1       | $\perp$   | 1        | $\perp$   |

| $\perp$ | $\perp$ | $\perp$   | $\perp$  | $\perp$   |

| x      | NOT(x)  |

|--------|---------|

| 0      | 1       |

| 1      | 0       |

| $\bot$ | $\perp$ |

|        |         |

Figure 2.6: Ternary extensions for common gates.

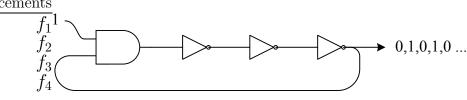

#### 2.2.2 Fixed Point

The goal of functional analysis is to determine what output values a circuit produces in response to Boolean input values. Of course, if the circuit is cyclic, we cannot be sure that it settles to a stable state. Consider the inverter ring shown in Figure 2.7. With x = 1, the ring will probably oscillate, with the output z alternating between 0 and 1, as shown in Figure 2.8. Within the ternary framework, all instability is hidden beneath the  $\perp$  values. This is illustrated with the inverter chain in Figure 2.9.

The following theorem shows that once a definite value is assigned to an internal wire, this value persists for the duration of the interval (so long as the input values are held constant). Furthermore, the order of gate evaluations is irrelevant; the final

Figure 2.7: An inverter ring.

outcome – which internal wires are assigned definite values, and what these values are – is the same regardless. The analysis terminates at a **fixed point**: in this state, every gate evaluation agrees with the value on its output wire, so there are no further changes. Of course, the term "fixed point" is somewhat paradoxical: with  $\perp$  values, the state includes signals that are potentially unstable. PSfrag replacements

Figure 2.8: In the Boolean framework, the inverter ring oscillates. PSfrag replacements

Figure 2.9: In the ternary framework, the values are unknown/undefined.

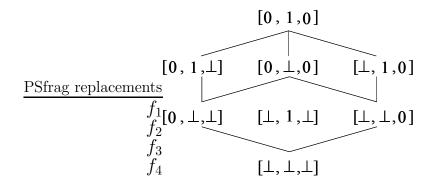

**Theorem 2.1** With all the internal signals assigned an initial value  $\perp$ , for a given set of Boolean values applied to the inputs and held constant, the analysis terminates at a unique fixed point.

**Proof:** Call the values assumed by the internal variables  $W = (w_1, \ldots, w_n)$  the state. Beginning from the initial state  $W_0 = (\perp, \ldots, \perp)$ , the circuit evolves through a sequence,

$$W_0, W_1, W_2, \ldots$$

Since each gate update consists of a change  $\perp \rightarrow \{0,1\}$ , the sequence of states is

ordered,

$$W_0 \sqsubseteq W_1 \sqsubseteq W_2 \sqsubseteq \dots$$

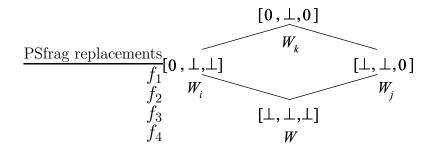

Since the number of states is finite, clearly the computation terminates at some fixed point. This is illustrated in Figure 2.10.

It remains to show that this fixed point is unique. To do so, we argue that the order of updates is irrelevant. Indeed, from a given state W, if we have a choice of immediate successor states  $W_i$  and  $W_j$ , then the partial join  $W_k = W_i \sqcup W_j$  exists and is an immediate successor state to both  $W_i$  and  $W_j$ . This is illustrated in Figure 2.11. With the initial state  $(\perp, \ldots, \perp)$  as the base case, a simple inductive argument suffices to show that all states have a common successor. This common successor must be a fixed point.

Figure 2.10: The computation terminates at a fixed point.

Figure 2.11: The order of updates is irrelevant.

#### 2.2.3 Explicit Analysis

The analysis strategy for specific Boolean input values might be termed *simulation*: we apply inputs and follow the evolution of the circuit. The goal of **functional analysis** is to determine *what* values appear; the goal of **timing analysis** is to determine *when* these values appear.

For functional analysis, Theorem 2.1 tells us that the gates may be evaluated in any order. We simply apply the inputs and follow the signals as they propagate; gates are evaluated when new signals arrive. Once a gate evaluates to a definite Boolean value, it is not evaluated again. Once the analysis terminates, if there are  $\perp$  values on the outputs, we conclude that the circuit does not behave combinationally.

For timing analysis, we establish an upper bound on the *arrival times* of definite Boolean values for internal signals. We always evaluate gates in the order that signals arrive, ensuring that we know the earliest time that a signal value becomes known. When evaluating a gate, we use only present and past input values, not future values.

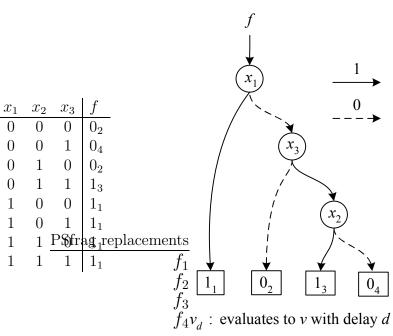

We illustrate analysis with a collection of examples: first two (acyclic) circuit fragments; then a non-combinational cyclic circuit; and finally a combinational cyclic circuit. We assume that all gates have unit delay, and that the primary inputs arrive at time 0.

#### Example 2.1

Consider the circuit fragment shown in Figure 2.12. It consists of four gates: an AND gate  $g_1$ , an OR gate  $g_2$ , an AND gate  $g_3$ , and an OR gate  $g_4$ :

$$g_1(x_1, y_1) = x_1 y_1,$$

$$g_2(x_2, y_2) = x_2 + y_2,$$

$$g_3(x_3, y_3) = x_3 y_3,$$

$$g_4(x_1, y_4) = x_1 + y_4.$$

This circuit illustrates the concept of *false paths*. From a topological perspective,

Figure 2.12: A circuit fragment.

there exists a path from point A to point B in this circuit. However, from a functional standpoint, this path is never *sensitized*. To see this, consider specific input values:

- With  $x_1 = 0$ , the path is blocked at gate  $g_1$ .

- With  $x_2 = 1$ , the path is blocked at gate  $g_2$ .

- With  $x_3 = 0$ , the path is blocked at gate  $g_3$ .

- With  $x_1 = 1$ , the path is blocked at gate  $g_4$ .

For any combination of input values, we know what value appears at point B, and how long it takes for this value to appear, regardless of the signal at point A. Assuming that the gates  $g_1$ ,  $g_2$ ,  $g_3$  and  $g_4$  have uniform delay bounds of  $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_4$ , respectively, we can assert:

- With  $x_1 = 1$ , a value of 1 appears after  $t_4$  time units.

- With  $x_1 = 0$ , and  $x_3 = 0$ , a value of 0 appears after  $t_3 + t_4$  time units.

- With  $x_1 = 0$ ,  $x_3 = 1$ , and  $x_2 = 1$ , a value of 1 appears after  $t_2 + t_3 + t_4$  time units.

- With  $x_1 = 0$ ,  $x_3 = 1$ , and  $x_2 = 0$ , a value of 0 appears after  $t_1 + t_2 + t_3 + t_4$  time units.

Further assuming a unit delay model (i.e.,  $t_1 = t_2 = t_3 = t_4 = 1$ ), we obtain the analysis results in Table 2.1. Subscripts on the values indicate the arrival times.

26

| $x_1$ | $x_2$ | $x_3$ | f       |

|-------|-------|-------|---------|

| 0     | 0     | 0     | $0_{2}$ |

| 0     | 0     | 1     | $0_4$   |

| 0     | 1     | 0     | $0_{2}$ |

| 0     | 1     | 1     | $1_3$   |

| 1     | 0     | 0     | $1_{1}$ |

| 1     | 0     | 1     | $1_{1}$ |

| 1     | 1     | 0     | $1_{1}$ |

| 1     | 1     | 1     | $1_1$   |

Table 2.1: Analysis of the circuit fragment in Figure 2.12.

#### Example 2.2

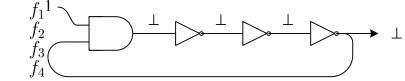

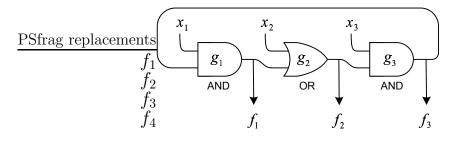

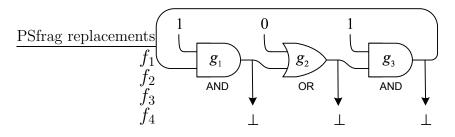

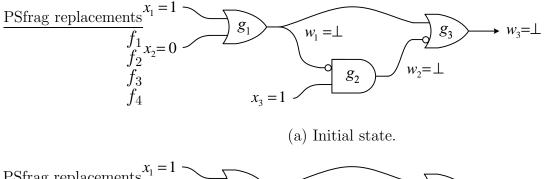

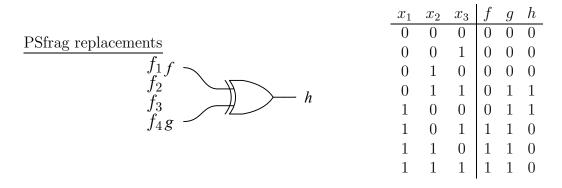

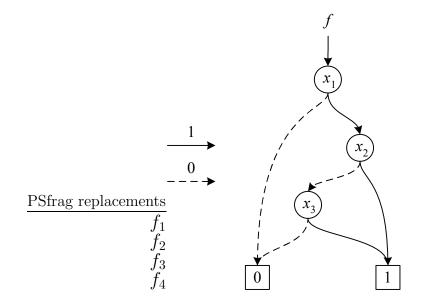

Consider the circuit shown in Figure 2.13, consisting of an AND gate  $g_1$ , an OR gate  $g_2$ , and an AND gate  $g_3$ , in a cycle. By inspection, note that if  $x_1 = 0$  then  $f_1$  assumes value 0 after one time unit; if  $x_2 = 1$  then  $f_2$  assumes value 1 after one time unit; and if  $x_3 = 0$  then  $f_3$  assumes value 0 after one time unit. But what happens if  $x_1 = 1$ ,  $x_2 = 0$  and  $x_3 = 1$ ? In this case, all the outputs equal  $\perp$ , as illustrated in Figure 2.14. The outcome for all eight cases is shown in Table 2.2.

Figure 2.13: A non-combinational cyclic circuit.

Figure 2.14: The circuit of Figure 2.13 with  $x_1 = 1$ ,  $x_2 = 0$  and  $x_3 = 1$ .

| $x_1$ | $x_2$ | $x_3$ | $f_1$                                                                                              | $f_2$   | $f_3$   |

|-------|-------|-------|----------------------------------------------------------------------------------------------------|---------|---------|

| 0     | 0     | 0     | $0_1$                                                                                              | $0_{2}$ | $0_1$   |

| 0     | 0     | 1     | $0_1$                                                                                              | $0_{2}$ | $0_3$   |

| 0     | 1     | 0     | $0_1$                                                                                              | $1_1$   | $0_1$   |

| 0     | 1     | 1     | $0_1$                                                                                              | $1_1$   | $1_2$   |

| 1     | 0     | 0     | $0_{2}$                                                                                            | $0_3$   | $0_1$   |

| 1     | 0     | 1     | $\perp$                                                                                            | $\perp$ | $\perp$ |

| 1     | 1     | 0     | $0_{2}$                                                                                            | $1_1$   | $0_1$   |

| 1     | 1     | 1     | $\begin{array}{c} 0_{1} \\ 0_{1} \\ 0_{1} \\ 0_{1} \\ 0_{2} \\ \bot \\ 0_{2} \\ 1_{3} \end{array}$ | $1_1$   | $1_{2}$ |

Table 2.2: Analysis of circuit in Figure 2.13.

In general, we would reject this circuit, since its outputs are not defined for the input assignment  $x_1 = 1$ ,  $x_2 = 0$  and  $x_3 = 1$ . However, if this particular assignment is in the "don't care" set, then the design would be valid.

#### Example 2.3

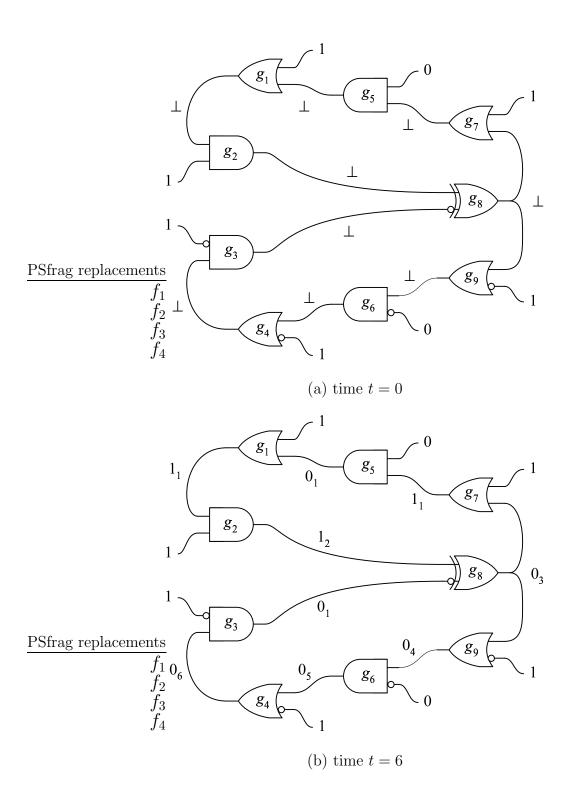

Consider the circuit in Figure 2.15 (a).

• Of the three gates, we see that initially only  $g_1$  evaluates to a definite value,

$$w_1 = g_1(x_1, x_2) = OR(1, 0) = 1.$$

We set the arrival time of  $w_1$  to be

$$t_1 = 1.$$

• With  $w_1$  defined, we see that  $g_2$  evaluates to a definite value,

$$w_2 = g_2(w_1, x_2) = \text{AND}(\text{NOT}(1), 1) = 0.$$

We set arrival time of  $w_2$  to be

$$t_2 = 1 + t_1 = 2.$$

• At this point in the execution of the algorithm,  $w_1$  and  $w_2$  have been assigned definite values. However,  $w_1$  has an earlier arrival time. Evaluating  $g_3$  at time 1,

$$w_3 = g_3(w_1, w_2) = OR(1, NOT(\bot)) = 1.$$

We set the arrival time of  $w_3$  to be

$$t_3 = 1 + t_1 = 2.$$

The final values of  $w_1, w_2, w_3$  are shown in Figure 2.15 (b). Subscripts indicate the arrival times.

(b) Final state.

Figure 2.15: Example 2.3 Subscripts on the values of the internal variables indicate the arrival times.

The salient point of this example is that the algorithm tracks the arrival times of signals, and establishes the earliest possible set of controlling signals. If gate  $g_3$  had been evaluated after both  $w_1$  and  $w_2$  had been determined, we might have concluded that its arrival time was 3 time units instead of 2.

#### Example 2.4

Consider the circuit in Figure 2.16. Suppose that we apply inputs  $x_1 = 1, x_2 = 0, x_3 = 1$ , as shown in Part (a). Gates  $g_1, g_3, g_5$  and  $g_7$  produce outputs of 1, 0, 0, and 1, respectively, after one time unit. Gate  $g_2$  produces an output of 1 after two time units. Gate  $g_8$  produces an output of 0 after three time units. Gate  $g_9$  produces

an output of 0 after four time units. Gate  $g_6$  produces an output of 0 after five time units. Finally, gate  $g_4$  produces an output of 0 after six time units. The circuit after six time units is shown in Figure 2.16 (b).

The analysis for all eight input combinations is summarized in Table 2.3. We see that the maximum delay of the circuit is six time units.

| $x_1$ | $x_2$ | $x_3$ | $g_1$   | $g_2$ | $g_3$ | $g_4$   | $g_5$ | $g_6$ | $g_7$   | $g_8$ | $g_9$ |

|-------|-------|-------|---------|-------|-------|---------|-------|-------|---------|-------|-------|

|       | 0     |       |         |       |       |         |       |       |         |       |       |

| 0     | 0     | 1     | $1_1$   | $0_1$ | $1_4$ | $1_3$   | $0_1$ | $1_2$ | $0_6$   | $0_5$ | $1_1$ |

| 0     | 1     | 0     | $0_6$   | $0_1$ | $1_2$ | $1_1$   | $0_5$ | $0_1$ | $0_4$   | $0_3$ | $1_1$ |

| 0     | 1     | 1     | $1_1$   | $0_1$ | $0_3$ | $0_2$   | $1_6$ | $0_1$ | $1_5$   | $1_4$ | $1_1$ |

| 1     | 0     | 0     | $0_{2}$ | $0_3$ | $0_1$ | $1_{1}$ | $0_1$ | $1_6$ | $1_{1}$ | $1_4$ | $1_5$ |

| 1     | 0     | 1     | $1_1$   | $1_2$ | $0_1$ | $0_6$   | $0_1$ | $0_5$ | $1_{1}$ | $0_3$ | $0_4$ |

| 1     | 1     | 0     | $1_3$   | $1_4$ | $0_1$ | $1_1$   | $1_2$ | $0_1$ | $1_{1}$ | $0_5$ | $0_6$ |

| 1     | 1     | 1     | $1_{1}$ | $1_2$ | $0_1$ | $0_2$   | $1_2$ | $0_1$ | $1_1$   | $0_3$ | $0_4$ |

Table 2.3: Analysis summary for the circuit of Figure 2.3. Subscripts on the output values indicate arrival times.

#### 2.2.4 Complexity

In the analysis, we evaluate a gate whenever a new Boolean signal arrives on one of its inputs. In the worst case, we could evaluate a gate with fan-in d as many as dtimes. Given a circuit with m primary inputs and n gates, each with fan-in d, there are O(dn) gate evaluations. In addition, for timing analysis, we must maintain a sorted list of arrival times. This contributes a complexity factor of  $O(n \log_2 n)$ .

We could perform the analysis explicitly for every assignment of input values. However, such an exhaustive approach is simply not tractable for most real circuits: with n variables there would be  $2^n$  input combinations to analyze separately. In Chapter 4 we describe an efficient analysis algorithm based on *symbolic* techniques.

Figure 2.16: The circuit of Figure 2.3 with inputs  $x_1 = 1, x_2 = 0, x_3 = 1$ . Subscripts on the output values indicate arrival times.

# Chapter 3 Theory

In theory there is no difference between theory and practice, but in practice there is. – Yogi Berra (1925–)

Theoreticians are preoccupied with *classifying* and *characterizing* problems in general terms. They discuss the relationships among complexity classes, and prove bounds on the size of circuits. However, somewhat to their embarrassment, they offer very little help in proving or disproving the optimality of specific circuits. There have been a handful of papers, dating back to the 1960's, describing approaches for finding optimal multi-level circuit designs [10], [11], [20], but these have limited applicability: the largest circuits that these methods can hope to tackle have 4 (or perhaps 5) input variables.

Lower bounds on circuit size are notoriously difficult to establish. In fact, such proofs are related to fundamental questions in computer science, such as the separation of the P and NP complexity classes. (To prove that  $P \neq NP$  it would suffice to find a class of problems in NP that cannot be computed by a polynomially sized circuit.) Much of the recent work in circuit complexity has been spurred by these open problems [1].

All existing lower bounds on circuit size are linear in the number of variables [1]. In 1949, Shannon showed by a straight forward counting argument that nearly *all* functions require circuits with an exponential number of gates [40]. Yet there is no known *explicit* example [48]. Given these limitations, how can we hope to justify our general claim that feedback can be used to optimize circuits? In this section, we assume the theoretician's mantle and *prove* that some cyclic designs are smaller than equivalent acyclic ones, based on the best lower-bound techniques that we know.

# 3.1 Criteria for Optimality

Any assertion of optimality rests on a restricted circuit model. Indeed, with gates of arbitrary size and complexity, any function can be implemented with a single "gate." We restrict the scope of gates in two ways. The first way is to bound the *fan-in*, as shown in Figure 3.1 (a). Each gate can have at most d inputs, for some finite d. The second way is to restrict the type of gate. For instance, we can limit ourselves to so-called AON gates: AND gates with the inputs and output possibly negated. An example of such a gate is shown in Figure 3.1 (b). The general form of the Boolean function realized by an AON gate is

$$g(x_1, x_2, \dots, x_d) = (x_1 \oplus c_1) \cdot (x_2 \oplus c_2) \cdots (x_d \oplus c_d) \oplus c_{d+1}$$

where  $c_1, \ldots, c_{d+1}$  are arbitrary choices of 0 and 1. (Multiplication represents AND, addition represents OR, and  $\oplus$  represents XOR.) The fan-in d may or may not be limited.

Figure 3.1: Restricting the scope of gates. (a) Bound the fan-in. (b) Use AND gates (with the inputs and output possibly negated).

In this chapter, we often represent functions in **XNF**, a canonical form consisting of XOR and AND operations. This form has advantages: since it is canonical, we need not concern ourselves with simplifying the expressions. Furthermore, the dependence of a function on its variables is explicit. See Appendix A for a discussion of this representation.

Our general strategy in the following constructions is to present a cyclic circuit that is optimal in the number of gates, and then prove a lower bound on the size of any acyclic circuit implementing the same functions. The argument for the optimality of the cyclic circuit rests on two properties:

**Property 3.1** Each of the output functions depends on all its variables.

**Property 3.2** The output functions are distinct.

The cyclic circuit is shown to be optimal according to the following trivial claim (true *regardless* of the gate model):

**Claim 3.1** A circuit implementing m distinct functions consists of at least m gates.

### 3.2 Fan-in Lower Bound

Our lower bound on the size of an acyclic circuit is formulated as a fan-in argument. The essence of the argument was presented by Rivest [35], although we present it in a more general form.

A circuit can only compute a function of a given set of input variables if it "sees" all of them. For example, in Figure 3.2, gate  $g_2$  can compute a function of  $x_1, x_2$  and  $x_3$ ;  $g_1$  cannot compute a function of  $x_3$  since it does not see  $x_3$ . In an acyclic circuit, there is a partial ordering among the gates: if a gate  $g_i$  depends on a gate  $g_j$ , directly or indirectly, then  $g_j$  cannot depend on  $g_i$ , directly or indirectly. With a partial ordering on the output functions, there must be at least one output function at the top which depends upon no other. If this function depends on v input variables, the gate producing it must be the root of a tree that sees all these v variables as leaves. The lower bound is based on a calculation of the minimum number of gates in this tree.

Figure 3.2: A gate can only compute functions of variables that it "sees".

**Claim 3.2** An acyclic circuit implementing m distinct output functions, each depending on v input variables, consisting of gates with fan-in at most d has at least

$$\left\lceil \frac{v-1}{d-1} \right\rceil + m - 1$$

gates.

**Proof:** Consider a connected directed acyclic graph (DAG). Call nodes with no in-coming edges *leaves*, and all other nodes *internal* nodes. We show, by a simple inductive argument, that a connected DAG with k internal nodes, each with indegree at most d, has at most k(d-1) + 1 leaves. Obviously, a graph consisting of a single such internal node has at most d leaves. Suppose an internal node with indegree at most d is added to a connected DAG. If the resulting graph is to be a *connected* DAG, the new node can replace an existing leaf or it can be attached to an existing internal node. The former case is illustrated with node  $g_1$  in Figure 3.3, and the latter with node  $g_2$ . In both cases there is a net gain of at most d-1 leaves. We conclude that connected DAG with k internal nodes has at most

$$d + (k - 1)(d - 1) = k(d - 1) + 1$$

leaves, as expected. Suppose that a connected DAG has v leaves. Since

Figure 3.3: Adding a node with in-degree d to a connected DAG results in net gain of at most d - 1 leaves.

$$v \le k(d-1) + 1,$$

the number of internal nodes k is bounded by

$$k \ge \left\lceil \frac{v-1}{d-1} \right\rceil.$$

Now, in an acyclic circuit implementing m output functions, at least one of the output functions depends on no other. By the argument above, this output function requires at least

$$\left\lceil \frac{v-1}{d-1} \right\rceil$$

gates. With *distinct* output functions, each output function must emanate from a different gate, so at least m-1 gates are required to implement the remaining m-1 functions.

36

# 3.3 Improvement Factor

Suppose that we have a cyclic circuit with m gates, each with fan-in at most d, that implements m distinct functions, each of which depends on all v input variables. Call the *improvement factor* the ratio of size of the cyclic circuit to the lower bound on the size of the acyclic circuit:

$$\frac{\text{size of cyclic}}{\text{size of acyclic}} = \frac{m}{\left\lceil \frac{v-1}{d-1} \right\rceil + m - 1}.$$

With an improvement factor of C, we can say that our cyclic circuit is C times the size of any equivalent acyclic circuit.

Claim 3.3 The improvement factor is bounded below by  $\frac{1}{2}$ .

**Proof:** For a given d, the improvement factor is minimized if the term

$$\frac{v-1}{d-1}$$

in the denominator is maximized. Now, the number of variables v in a cyclic circuit is at most m(d-1), and this is achieved if all the gates have fan-in d. For such a circuit,

$$\frac{m}{\left\lceil m - \frac{1}{d-1} \right\rceil + m - 1} = \frac{m}{2m - 1} \ge \frac{1}{2}.$$

## 3.4 Examples

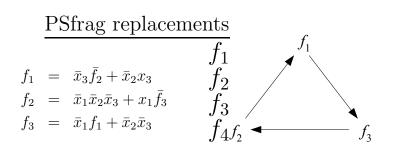

Consider the example shown in Figure 3.4, due to Rivest [35]. We first verify that this circuit is combinational. For gate  $g_1$ , an AND gate,  $x_1 = 0$  is a controlling value.

Figure 3.4: A cyclic combinational circuit with 3 inputs, due to Rivest [35].

Setting  $x_1 = 0$  we have

$$f_{1} |_{\bar{x}_{1}} = 0,$$

$$f_{2} |_{\bar{x}_{1}} = f_{1} + x_{2} = x_{2},$$

$$f_{3} |_{\bar{x}_{1}} = f_{2} x_{3} = x_{2} x_{3},$$

$$f_{4} |_{\bar{x}_{1}} = f_{3} + 0 = x_{2} x_{3},$$

$$f_{5} |_{\bar{x}_{1}} = f_{4} x_{2} = x_{2} x_{3},$$

$$f_{6} |_{\bar{x}_{1}} = f_{5} + x_{3} = x_{3}.$$

All outputs assume definite Boolean values. For gate  $g_4$ , an OR gate,  $x_1 = 1$  is a controlling value. Setting  $x_1 = 1$ , we have

$$f_{4} |_{x_{1}} = 1,$$

$$f_{5} |_{x_{1}} = f_{4} x_{2} = x_{2},$$

$$f_{6} |_{x_{1}} = f_{5} + x_{3} = x_{2} + x_{3},$$

$$f_{1} |_{x_{1}} = f_{6} 1 = x_{2} + x_{3},$$

$$f_{2} |_{x_{1}} = f_{1} + x_{2} = x_{2} + x_{3},$$

$$f_{3} |_{x_{1}} = f_{2} x_{3} = x_{3}.$$

Again, all outputs assume definite Boolean values. Since  $x_1$  must either have value 0 or value 1, we conclude that the network is combinational. We assemble the output functions from these two cases:

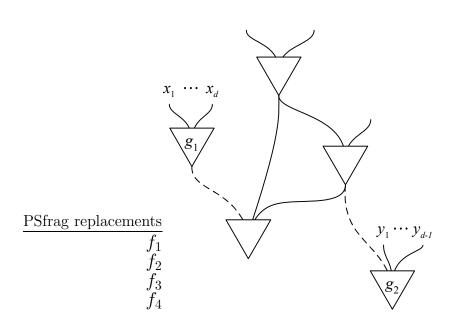

Rivest presented a more general version of this circuit. For any odd integer n greater than 1, the general circuit consists of n two-input AND gates alternating with ntwo-input OR gates in a single cycle, with inputs  $x_1, \ldots, x_n$  repeated, as shown in Figure 3.5. Analyzing the general circuit in the same manner as above, we find that

Figure 3.5: A cyclic combinational circuit with n inputs (for any odd  $n \ge 3$ ) due to Rivest.

it implements the functions

$$f_{1} = x_{1}(x_{n} + x_{n-1}(\cdots(x_{3} + x_{2})\cdots))$$

$$f_{2} = x_{2} + x_{1}(x_{n} + \cdots(x_{4}x_{3})\cdots)$$

$$\vdots$$

$$f_{2n} = x_{n} + x_{n-1}(x_{n-2} + \cdots(x_{2}x_{1})\cdots).$$

Note that the functions are symmetrical with respect to a cyclic permutation of the variables.

#### 3.4.1 Optimality

To show that circuit is optimal, we must show that it satisfies Properties 3.1 and 3.2.

1. To show that each function depends on all n input variables, we note that in the parenthesized expression, each variable appears exactly once. Without loss of generality, consider the *i*-th function  $f_i$  in the list, for an odd *i*, and consider the *j*-th variable appearing in its expression, from the left-hand side. To show the dependence on this variable, set each variable preceding a product to 1, and each variable preceding a sum to zero, beginning on the left-hand side, until we arrive at  $x_j$ . Set the variable following  $x_j$  to 1 and all variables following that to 0. The result is

$$f_i = 1(0 + 1(0 + \dots + x_i(1 + 0(0 + 0(\dots))))) = x_i.$$

2. To show that all the functions are distinct, we exhibit an assignment that sets any chosen function to 0 if it is odd-numbered (to 1 if it is even-numbered), while setting all the other functions to 1 (to 0, respectively). Without loss of generality, consider function  $f_i$ , for an odd  $i \leq n$ . This function is the output of an AND gate with input  $x_i$ . Set  $x_i$  to 0 and set all the other the variables to 1. Clearly,  $f_i$  has value 0 while all the other functions have value 1 in this case.

(Rivest stated these conditions without proof.)

#### 3.4.2 Acyclic Lower Bound

Note that the Rivest circuit has n input variables and implements 2n distinct output functions with 2n fan-in 2 gates. According to Claim 3.2, an acyclic circuit implementing the same functions requires at least

$$\left\lceil \frac{n-1}{2-1} \right\rceil + 2n - 1 = 3n - 2$$

fan-in 2 gates. For large n, the improvement factor is

$$\frac{\text{size of cyclic}}{\text{size of acyclic}} = \frac{2n}{3n-2} \approx \frac{2}{3}.$$

Rivest's cyclic circuit is two-thirds the size of any acyclic circuit implementing the same functions.

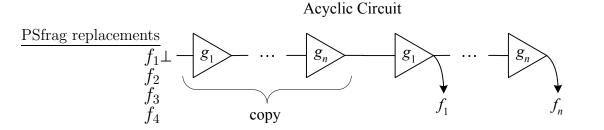

Given a circuit with a single cycle, we can always obtain a corresponding acyclic version by breaking the feedback and doubling the length of the chain, as shown in Figure 3.6. (The input  $\perp$  indicates any constant value.)

# Cyclic Circuit

Figure 3.6: Obtaining an equivalent acyclic circuit from a cyclic circuit.

In general, this will not yield an optimal acyclic circuit. However, in the case of Rivest's circuit, the bound of 3n - 2 is, in fact, tight. To obtain an acyclic circuit with 3n - 2 gates, we break the cycle and prepend a copy of the last n - 2 gates. For n = 3, we simply prepend an OR gate with inputs  $x_2$  and  $x_3$ , as shown in Figure 3.7.

Rivest's circuit is also optimal seen from a different perspective. The circuit consists of AON gates, and yet none of the output functions are implementable with a single AON gate, regardless of the fan-in. Thus, any acyclic circuit implementing the functions requires at least one more gate.

Figure 3.7: An acyclic circuit implementing the same functions as the circuit in Figure 3.4.

### 3.4.3 A Generalization

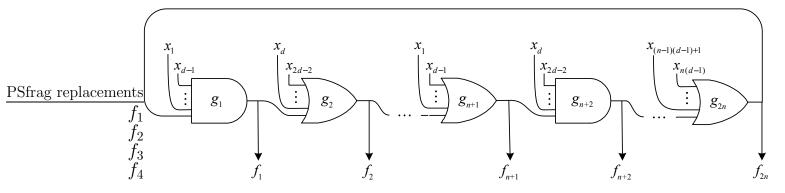

We note that Rivest's circuit can be generalized to AND and OR gates with arbitrary fan-in. The circuit, shown in Figure 3.8, consists of 2n fan-in d AND/OR gates, with n(d-1) inputs repeated, for  $n \ge 3$ , n odd, and  $d \ge 2$ .

Figure 3.8: A generalization of Rivest's circuit to gates with fan-in greater than 2.

This circuit produces outputs

$$f_{1} = y_{1}(y_{n} + y_{n-1}(\cdots(y_{3} + y_{2})\cdots))$$

$$f_{2} = y_{2} + y_{1}(y_{n} + \cdots(y_{4}y_{3})\cdots)$$

$$\vdots$$

$$f_{2n} = y_{n} + y_{n-1}(y_{n-2} + \cdots(y_{2}y_{1})\cdots),$$

where

$$y_1 = x_1 \cdots x_{d-1}$$

$y_2 = x_d + \cdots + x_{2d-2}$

$\vdots$

$y_n = x_{(n-1)(d-1)+1} + \cdots + x_{n(d-1)}.$

It may be shown that all 2n functions are distinct, and that each depends on all n(d-1) input variables.

#### 3.4.4 Variants

We note that many different circuits of the same general form as Rivest's example exist. In Figure 3.9, we show a circuit with 4 variables and 8 gates in a single cycle. As with Rivest's circuit, this one produces distinct output functions, each of which depends on all the variables.

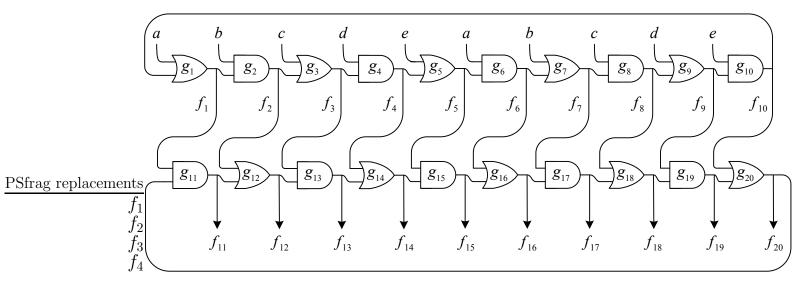

A more intriguing example is shown in Figure 3.10. It consists of two copies of Rivest's circuit with the outputs of the first fed as inputs into the second. Although not shown here, we assert that this circuits produces 20 functions are distinct, and each depends on all 5 variables.

Figure 3.9: A circuit with the same properties as Rivest's example.

Figure 3.10: A pair of Rivest circuits, n = 5, stacked.

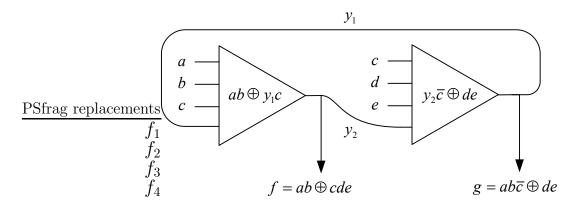

# 3.5 A Minimal Cyclic Circuit with Two Gates

We provide an example of a circuit with the same property as Rivest's circuit, but with only two gates. The circuit, shown in Figure 3.11, consists of two fan-in 4 gates of the form

$$g(w, x, y, z) = wx \oplus yz$$

connected in a cycle with 5 inputs, a, b, c, d, e. The circuit computes f and g:

$$f = ab \oplus gc$$

$$g = f\bar{c} \oplus de.$$

To verify that the circuit is combinational, note that if c = 0, f assumes a definite value. We have

$$f|_{\bar{c}} = ab \oplus g 0 = ab$$

$$g|_{\bar{c}} = f1 \oplus de = ab \oplus de$$

Similarly, if c = 1, then g also assumes a definite value. We have

$$g|_{c} = f 0 \oplus de = de$$

$$f|_{c} = ab \oplus g 1 = ab \oplus de.$$

Assembling the output functions, we obtain

$$f = \bar{c} \cdot f |_{\bar{c}} + c \cdot f |_{c} = ab \oplus cde$$

$$g = \bar{c} \cdot g |_{\bar{c}} + c \cdot g |_{c} = ab\bar{c} \oplus de.$$

With the functions thus written in XNF form, we can readily assert that f and g are distinct and that each depends on all 5 variables. Now, consider an acyclic circuit, also with fan-in 4 gates, that computes the same functions. Since a single fan-in 4 gate cannot possibly compute a function of 5 variables, we conclude that the acyclic circuit must have 3 gates.

Figure 3.11: A cyclic circuit with two gates.

# 3.6 Circuits with Multiple Cycles

In this section, we present examples of cyclic circuits with multiple cycles, culminating with the main result of this section: a cyclic circuit that is one-half the size of any equivalent acyclic circuit.

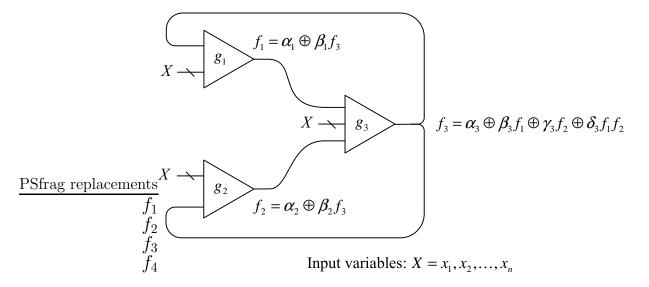

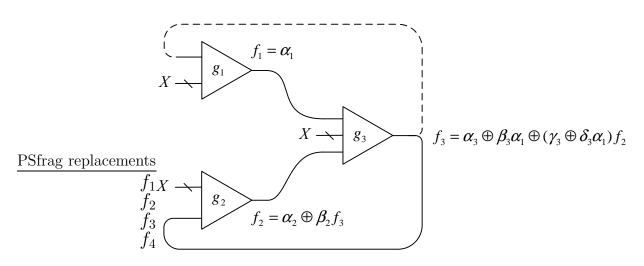

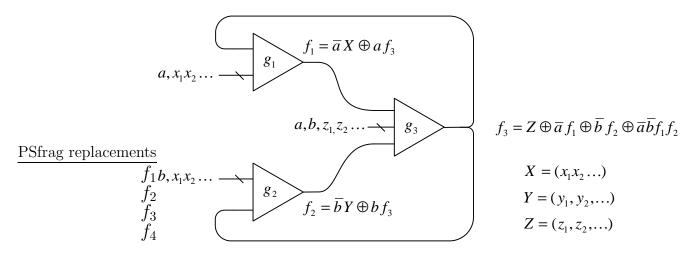

#### 3.6.1 A Cyclic Circuit with Two Cycles

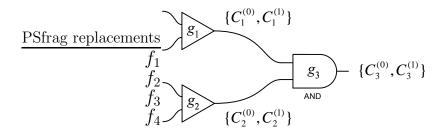

Consider the circuit shown in Figure 3.12, written in a general form. The inputs are  $x_1, \ldots, x_n$ , grouped together in the figure as X. (A diagonal line across a line indicates that it represents multiple wires.) There are three gates, connected in a

configuration consisting of two cycles:

$$f_1 = \alpha_1 \oplus \beta_1 f_3$$

$$f_2 = \alpha_2 \oplus \beta_2 f_3$$

$$f_3 = \alpha_3 \oplus \beta_3 f_1 \oplus \gamma_3 f_2 \oplus \delta_3 f_1 f_2$$

where the  $\alpha$ 's,  $\beta$ 's,  $\gamma$ 's, and  $\delta$ 's are arbitrary functions of the input variables.

Figure 3.12: A cyclic circuit with two cycles.

#### 3.6.2 Analysis in Arbitrary Terms

We analyze this circuit with the goal of obtaining a necessary and sufficient condition for combinationality, as well as expressions for the gate outputs in terms of the inputs. We proceed on a case basis.

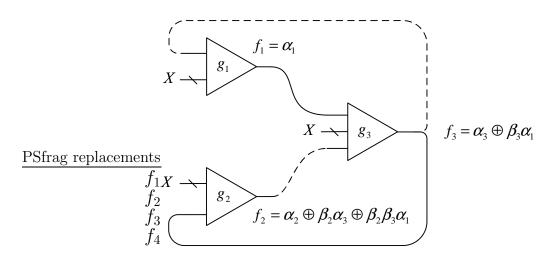

Case I

Suppose that for some X,  $\beta_1 = 0$ . In this case  $f_1$  assumes the definite value  $\alpha_1$ . This situation is shown in Figure 3.13. Now suppose further that  $\gamma_3 \oplus \delta_3 \alpha_1 = 0$ . In this case,  $f_3$  assumes a definite value of  $\alpha_3 \oplus \beta_3 \alpha_1$ . Given this value for  $f_3$ ,  $f_2$  assumes a definite value of  $\alpha_2 \oplus \beta_2 \alpha_3 \oplus \beta_2 \beta_3 \alpha_1$ . This situation is shown in Figure 3.14. We conclude that the functions assume definite values if  $\beta_1 = 0$  and  $\gamma_3 \oplus \delta_3 \alpha_1 = 0$ .

Figure 3.13: The circuit of Figure 3.12 if  $\beta_1 = 0$ .

Figure 3.14: The circuit of Figure 3.12 if  $\beta_1 = 0$  and  $\gamma_3 \oplus \delta_3 \alpha_1 = 0$ .

#### Case II

A symmetrical analysis shows that the functions  $f_1, f_2$  and  $f_3$  assume definite values if  $\beta_2 = 0$  and  $\beta_3 \oplus \delta_3 \alpha_2 = 0$ .

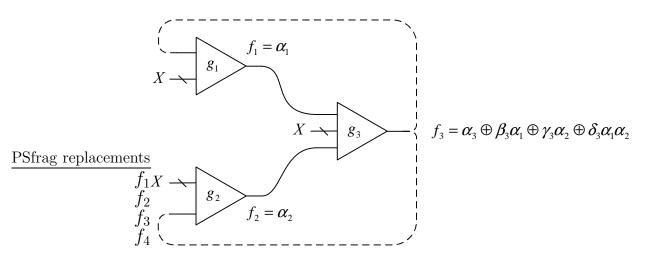

#### Case III

Suppose that for some X, we have  $\beta_1 = 0$  and  $\beta_2 = 0$ . In this case  $f_1$  and  $f_2$  assume definite values of  $\alpha_1$  and  $\alpha_2$ , respectively. Given these values for  $f_1$  and  $f_2$ ,  $f_3$  assumes a definite value of  $\alpha_3 \oplus \beta_3 \alpha_1 \oplus \gamma_3 \alpha_2 \oplus \delta_3 \alpha_1 \alpha_2$ . This situation is shown in Figure 3.15.

Figure 3.15: The circuit of Figure 3.12 if  $\beta_1 = 0$  and  $\beta_2 = 0$ .

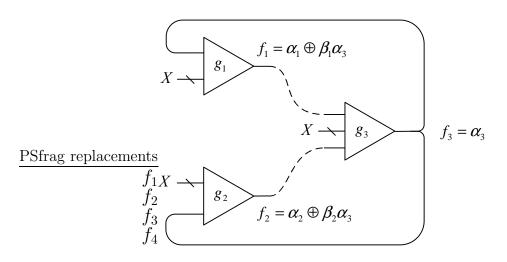

#### Case IV

Suppose that  $\beta_3 = \gamma_3 = \delta_3 = 0$ . In this case  $f_3$  assumes the definite value  $\alpha_3$ . Given this value for  $f_3$ ,  $f_1$  and  $f_2$  assume the definite values  $\alpha_1 \oplus \beta_1 \alpha_3$  and  $\alpha_2 \oplus \beta_2 \alpha_3$ , respectively. This situation is shown in Figure 3.16.

$$c_1 = \overline{\beta_1} \cdot \overline{(\gamma_3 \oplus \delta_3 \alpha_1)}, \qquad (3.1)$$

$$c_2 = \overline{\beta_2} \cdot \overline{(\beta_3 \oplus \delta_3 \alpha_2)}, \qquad (3.2)$$

$$c_3 = \overline{\beta_1} \cdot \overline{\beta_2}, \tag{3.3}$$

$$c_4 = \overline{\beta_3} \cdot \overline{\gamma_3} \cdot \overline{\delta_3}. \tag{3.4}$$

Figure 3.16: The Circuit of Figure 3.12 if  $\beta_3 = \gamma_3 = \delta_3 = 0$ .

We conclude that the circuit is combinational iff

$$C = c_1 + c_2 + c_3 + c_4$$

holds. If C holds, then the functions have values

$$f_1 = c_1\alpha_1 + c_2(\alpha_1 \oplus \beta_1\alpha_3 \oplus \beta_1\gamma_3\alpha_2) + c_3\alpha_1 + c_4(\alpha_1 \oplus \beta_1\alpha_3)$$

$$(3.5)$$

$$f_2 = c_1(\alpha_2 \oplus \beta_2 \alpha_3 \oplus \beta_1 \beta_3 \alpha_1) + c_2 \alpha_2 + c_3 \alpha_2 + c_4(\alpha_2 \oplus \beta_2 \alpha_3)$$

$$(3.6)$$

$$f_3 = c_1(\alpha_3 \oplus \beta_3 \alpha_1) + c_2(\alpha_3 \oplus \gamma_3 \alpha_2) + c_3(\alpha_3 \oplus \beta_3 \alpha_1 \oplus \gamma_3 \alpha_2 \delta_3 \alpha_1 \alpha_2) + c_4 \alpha_3(3.7)$$

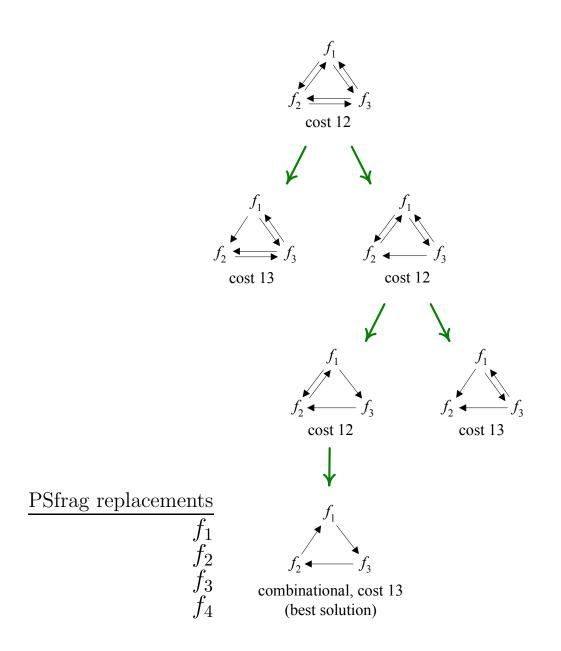

#### 3.6.3 A Circuit Three-Fifths the Size

Let's make the circuit of Figure 3.12 somewhat more concrete. Suppose that the inputs are  $a, b, x_1, x_2, \ldots, y_1, y_2, \ldots, z_1, z_2, \ldots$  Suppose that the gates are defined by

$$\alpha_1 = \bar{a}X, \qquad \alpha_2 = \bar{b}Y, \qquad \alpha_3 = Z,$$

where

$$X = x_1 x_2 \cdots, \qquad Y = y_1 y_2 \cdots, \qquad Z = z_1 z_2 \cdots,$$

and

$$\beta_1 = a, \qquad \beta_2 = b$$

$$\beta_3 = \bar{a}, \qquad \gamma_3 = \bar{b}, \qquad \delta_3 = \bar{a}\bar{b}$$

The resulting circuit is shown in Figure 3.17. For this circuit, the conditions defined

Figure 3.17: Variant of the circuit of Figure 3.12.

in Equations 3.1-3.4 evaluate to

$$c_1 = \bar{a}(b+X)$$

$$c_2 = \bar{b}(a+Y)$$

$$c_3 = \bar{a}\bar{b}$$

$$c_4 = ab$$

It may easily be verified that for every combination of values assigned to a and b, one of  $c_1, c_2, c_3, c_4$  is true. The functions defined in Equations 3.5–3.7 become

$$f_{1} = X \oplus a(X \oplus Y \oplus Z) \oplus abY$$

$$f_{2} = Y \oplus b(X \oplus Y \oplus Z) \oplus abX$$

$$f_{3} = X \oplus Y \oplus Z \oplus XY \oplus a(X \oplus XY) \oplus b(Y \oplus XY) \oplus abXY$$

With the functions expressed in XNF notation, we can assert that they are distinct and that each depends on all the variables.

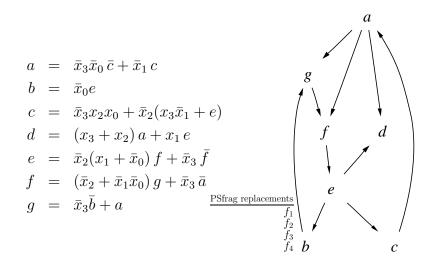

To make the situation more concrete, suppose that

$$X = c e g i, \qquad Y = d f h j, \qquad Z = k l.$$

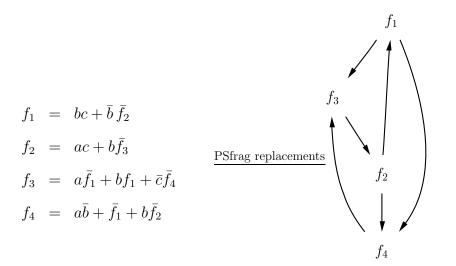

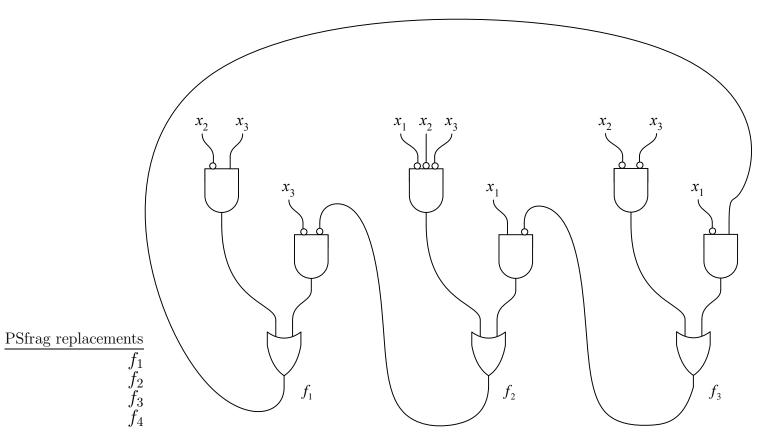

There are a total of 12 variables (a through l). Each gate has fan-in 6. This situation is shown in Figure 3.18.

Figure 3.18: Circuit of Figure 3.17 with 12 variables.

According to Claim 3.2, an acyclic circuit implementing the same functions requires at least

$$\left\lceil \frac{v-1}{d-1} \right\rceil + m - 1$$

gates, where v = 12 (the number of variables), d = 6 (the fan-in) and m = 3 (the number of functions). Thus

$$\left\lceil \frac{v-1}{d-1} \right\rceil + m - 1 = \left\lceil \frac{12-1}{6-1} \right\rceil + 3 - 1 = 5.$$

We conclude that the circuit in Figure 3.18 is at most  $\frac{3}{5}$  the size of any equivalent acyclic circuit.

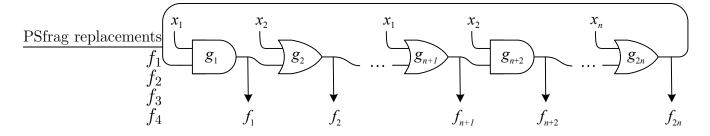

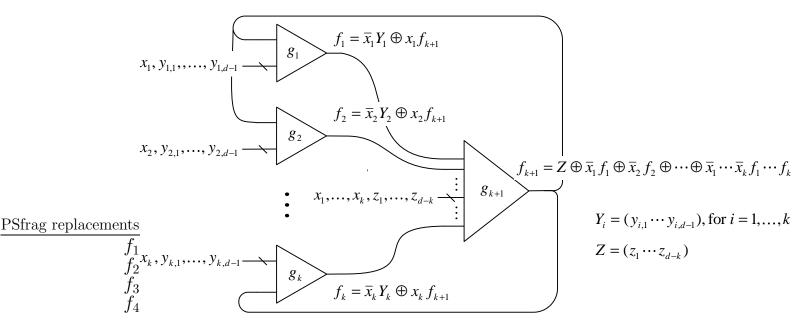

#### 3.6.4 A Circuit One-Half the Size

Consider the circuit shown in Figure 3.19, a generalization of the circuit in Figure 3.12 to k gates. We argue the validity of this circuit informally. On the one hand, for each

Figure 3.19: A generalization of the circuit of Figure 3.12.

variable  $x_i$ , if  $x_i = 0$  then the function  $f_i$  does not depend on  $f_{k+1}$ . On the other hand, if  $x_i = 1$ , then  $f_{k+1}$  does not depend on  $f_i$ . We conclude that none of the k cycles can be sensitized, and so the circuit is combinational. Now consider the function  $f_i$ implemented by each gate. With  $x_i = 0$ ,  $f_i$  depends on the variables  $y_{1,1}, \ldots, y_{1,d-1}$ . Since  $f_{k+1}$  depends on  $f_i$ , it also depends on these variables. Thus  $f_{k+1}$  depends all the variables  $y_{i,j}$  for  $i = 1, \ldots, k, j = 1, \ldots, d-1$ . With  $x_i = 1$ ,  $f_i$  depends on  $f_{k+1}$ ; hence it also depends on all these variables. We conclude that each function depends on all the variables.

With a fan-in of d, we have a total of

$$v = k(d-1) + d - 2k = (k+1)d - 3k$$

variables. We have

m = k + 1

gates. According to Claim 3.2, an acyclic circuit implementing the same functions requires at least

$$\left\lceil \frac{v-1}{d-1} \right\rceil + m - 1$$

gates. The improvement factor is,

$$\frac{m}{\left\lceil \frac{v-1}{d-1} \right\rceil + m - 1} = \frac{k+1}{\left\lceil \frac{(k+1)d-3k}{d-1} \right\rceil + k}$$

gates. Suppose that d = 3k, and that k is large. Then the ratio is

$$\frac{k+1}{\left\lceil\frac{3k^2-1}{3k-1}\right\rceil+k}\approx\frac{k}{k+k}=\frac{1}{2}\,.$$