#### Algorithms and Data Structures for Logic Synthesis and Verification Using Boolean Satisfiability

#### A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL

#### OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

John D. Backes

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy

Advisor: Marc D. Riedel

March, 2013

© John D. Backes 2013 ALL RIGHTS RESERVED

## Acknowledgements

At the time of writing this dissertation, I have spent nearly one third of my life studying at the University of Minnesota. Throughout this time I have met many brilliant and kind people that have not only shaped me academically, but characteristically into the person that I am today. I had the pleasure of working, learning, and becoming friends with Weikang Qian, Mustafa Altun, Hua Jiang, Sasha Karam, Phil Senum, Saket Gupta, Denis Kune, and many other students that are far more brilliant than I am. I would also like to thank Brian Isle, Tom Haigh, Jason Sonnek, Steve Harp, Todd Carpenter, and everyone at Adventium labs for giving me the opportunity to collaborate with them. I had an amazing experience working with Neha Rungta, Oksana Tkachuk, and Suzette Person at the NASA Ames Research Center. I feel obliged to mention my time spent in the Bay Area would not have been the same without Evan Long, Atil Işçen, Will Curran, Carrie Rebhuhn, and Josie Hunter.

I am lucky to have had such a great and positive committee for my dissertation. Sachin Sapatnekar taught my first course in graduate school: VLSI Design Automation. His teaching helped me tremendously when I began doing research in EDA. Kia Bazargan has given me great feedback on my research, and his mentorship during "Teaching Experiences in ECE" taught me how to best articulate my ideas. When it came time for me to ask professors to be on my committee, I wanted to find someone in the computer science department that had experience with Formal Methods. I cannot articulate accurately how grateful I am that I found Mike Whalen. Dr. Whalen's advice for my research has been extremely helpful, and I will never be able to adequately repay him for the doors of opportunity that he has opened for me in my professional life.

During my third semester of undergraduate study, I was frustrated to find that a new professor who was supposed to teach the recitation for my class on "Introduction to Digital System Design" did not show up to the first discussion. Apparently he had confused the names of the buildings "Akerman Hall" and "Amundson Hall" and was over 15 minutes late. To make it up to his students, he offered extra offices hours so we could get caught up on the material that was supposed to be taught during the discussion. While Professor Riedel's complete lack of temporal organization was sometimes frustrating in the future, the disorganization inadvertently caused the first of what would be many meetings over the next six years of my life. Marc's gleeful excitement when discussing technical concepts and unending positive feedback was what convinced me to go to graduate school. He routinely encouraged me to study whatever topics I found interesting. I am thoroughly convinced that I would not have been successful studying under the guidance of anyone else other than him.

Finally, I must thank my brilliant and beautiful girlfriend Caitlyn. She gave me relentless encouragment and had an endless amount of patience with me over the past three and a half years. She was truly my greatest discovery during graduate school.

## Dedication

To my parents,

who have always been able to find ways to satisfy all of my constraints...

#### Abstract

Boolean satisfiability (SAT) was the first problem to be proven to be NP-Complete. The proof, provided by Stephen Cook in 1971, demonstrated that inputs accepted by a non-deterministic Turing machine can be described by satisfying assignments of a Boolean formula. The reduction to SAT feels natural for a wealth of decision problems; this has motivated an immense amount of research into heuristics for solving SAT instances quickly. Over the past decade the performance of SAT solvers has improved tremendously, and as a consequence, real-world problems that were once thought to be intractable are now feasible in many cases.

In this thesis we discuss how some problems in logic synthesis and verification can be solved with Boolean satisfiability. The dissertation begins by discussing Cyclic Combinational Circuits. Cyclic Combinational Circuits are logic circuits that contain feedback, but exhibit no state behavior. Many functions can be implemented with fewer gates using a cyclic topology rather than an acyclic topology. A pivotal step in synthesizing these circuits is proving whether or not the resulting structure is actually combinational, and if not, how to modify the circuit to behave properly. This analysis can be elegantly cast as an instance of SAT. Furthermore, this thesis demonstrates how modern SAT-Based synthesis techniques can be used to generate cyclic structures, rather than just analyze them.

These SAT-Based synthesis techniques rely on augmenting proofs of unsatisfiability to generate circuit structures. These structures, called Craig Interpolants, and the proofs they are generated from are the focus of the second portion of this dissertation. Techniques are proposed for reducing the size of these interpolants, and then the use of proofs of unsatisfiability as an underlying data structure for synthesis is advocated.

Finally, the last portion of this thesis discusses some improvements to a new model checking algorithm known as Property Directed Reachability (PDR). This algorithm iteratively solves SAT instances representing discrete time frames of a sequential circuit in order to demonstrate that a state invariant exists.

# Contents

| A             | cknov | wledge        | ments                                | i             |

|---------------|-------|---------------|--------------------------------------|---------------|

| D             | edica | tion          |                                      | iii           |

| A             | bstra | $\mathbf{ct}$ |                                      | $\mathbf{iv}$ |

| $\mathbf{Li}$ | st of | Table         | 5                                    | x             |

| Li            | st of | Figur         | 25                                   | xi            |

| 1             | Ove   | erview        |                                      | 1             |

|               | 1.1   | Organ         | ization and Contributions            | 1             |

|               | 1.2   | Defini        | tions, Notation, and Common Concepts | 3             |

|               |       | 1.2.1         | Boolean Satisfiability               | 3             |

|               |       | 1.2.2         | Tsestin Transformation               | 7             |

| <b>2</b>      | Сус   | lic Cir       | cuits and Boolean Satisfiability     | 10            |

|               | 2.1   | Introd        | uction                               | 10            |

|               |       | 2.1.1         | Cyclic Combinational Circuits        | 10            |

|               |       | 2.1.2         | Prior and Related Work               | 14            |

|               |       | 2.1.3         | SAT-Based Synthesis                  | 16            |

|               | 2.2   | Circui        | t and Network Model                  | 17            |

|   |                | 2.2.1  | Gate Level vs. Functional Level Analysis                                                       | 19 |

|---|----------------|--------|------------------------------------------------------------------------------------------------|----|

|   | 2.3            | Functi | onal Dependencies                                                                              | 22 |

|   |                | 2.3.1  | Functional Dependencies with Craig Interpolation                                               | 25 |

|   |                | 2.3.2  | Generating Cyclic Functional Dependencies                                                      | 27 |

|   |                | 2.3.3  | General Method                                                                                 | 33 |

|   | 2.4            | Synthe | esizing Cyclic Dependencies                                                                    | 36 |

|   |                | 2.4.1  | Finding Support Sets                                                                           | 40 |

|   | 2.5            | Impler | mentation and Results                                                                          | 40 |

|   | 2.6            | Gate-I | Level Combinational Analysis Algorithm                                                         | 45 |

|   |                | 2.6.1  | Overview                                                                                       | 45 |

|   |                | 2.6.2  | Analysis Algorithm                                                                             | 47 |

|   | 2.7            | Proof  | of Correctness of Analysis                                                                     | 53 |

|   | 2.8            | Mappi  | ng Cyclic Combinational Circuits                                                               | 54 |

|   |                | 2.8.1  | Overview                                                                                       | 54 |

|   |                | 2.8.2  | Mapping Algorithm                                                                              | 57 |

|   | 2.9            | Proof  | of Correctness for Mapping                                                                     | 64 |

|   | 2.10           | Impler | mentation and Results                                                                          | 66 |

|   | 2.11           | Discus | sion $\ldots$ | 68 |

| 3 | $\mathbf{Red}$ | uction | of Interpolants for Logic Synthesis                                                            | 71 |

|   | 3.1            | Introd | uction                                                                                         | 71 |

|   | 3.2            | Backg  | round and Definitions                                                                          | 74 |

|   |                | 3.2.1  | DPLL Algorithm                                                                                 | 74 |

|   |                | 3.2.2  | Clause Learning and Incremental SAT                                                            | 75 |

|   |                | 3.2.3  | Resolution Proofs and Craig Interpolation                                                      | 77 |

|   | 3.3            | Propo  | sed Methodology                                                                                | 80 |

|   |                | 3.3.1  | Optimizations                                                                                  | 84 |

|   |                | 3.3.2  | Incremental Techniques                                                                         | 88 |

|   | 3.4            | Result                    | з                                                                                                   | 89         |

|---|----------------|---------------------------|-----------------------------------------------------------------------------------------------------|------------|

|   | 3.5            | Discus                    | ssion $\ldots$     | 94         |

| 4 | $\mathbf{Res}$ | olutio                    | n Proofs as a Data Structure For Logic Synthesis                                                    | 97         |

|   | 4.1            | Introd                    | luction                                                                                             | 97         |

|   | 4.2            | Relate                    | ed Work and Context                                                                                 | 99         |

|   | 4.3            | Gener                     | al Method                                                                                           | 100        |

|   | 4.4            | Correc                    | ctness                                                                                              | 101        |

|   | 4.5            | Imple                     | mentation and Results                                                                               | 105        |

|   | 4.6            | Discus                    | ssion                                                                                               | 107        |

| 5 | Usi            | ng Cul                    | bes of Non-state Variables With Property Directed Reacha                                            | <b>i</b> - |

|   | bilit          | $^{\mathrm{t}}\mathbf{y}$ |                                                                                                     | 108        |

|   | 5.1            | Introd                    | luction                                                                                             | 108        |

|   | 5.2            | Backg                     | round and Definitions                                                                               | 110        |

|   |                | 5.2.1                     | Definitions and Notation                                                                            | 110        |

|   |                | 5.2.2                     | Bounded Model Checking                                                                              | 111        |

|   |                | 5.2.3                     | Induction $\ldots$ | 112        |

|   |                | 5.2.4                     | Interpolation Based Model Checking                                                                  | 114        |

|   |                | 5.2.5                     | Property Directed Reachability                                                                      | 117        |

|   |                | 5.2.6                     | Property Directed Reachability Beyond State Variables                                               | 119        |

|   | 5.3            | Exten                     | ding Cubes To Gate Variables                                                                        | 120        |

|   |                | 5.3.1                     | General Concept                                                                                     | 120        |

|   |                | 5.3.2                     | Details for Ternary Valued Simulation                                                               | 123        |

|   | 5.4            | Exper                     | iment and Results                                                                                   | 125        |

|   |                | 5.4.1                     | Experiment Setup                                                                                    | 125        |

|   |                | 5.4.2                     | Results                                                                                             | 126        |

|   |                | 5.4.3                     | Other Heuristics We Tried                                                                           | 129        |

|   | 5.5            | Discus                    | ssion                                                                                               | 129        |

| 6  | Future Directions |                                                                                         |     |

|----|-------------------|-----------------------------------------------------------------------------------------|-----|

|    | 6.1               | Cyclic Combinational Circuits                                                           | 132 |

|    | 6.2               | Reducing Interpolants and Resolution Proofs $\ldots \ldots \ldots \ldots \ldots \ldots$ | 135 |

|    | 6.3               | Property Directed Reachability                                                          | 135 |

| Re | References        |                                                                                         |     |

# List of Tables

| 2.1 | Results of circuits synthesized with CYCLIFY and then optimized with     |     |

|-----|--------------------------------------------------------------------------|-----|

|     | ABC                                                                      | 42  |

| 2.2 | Runtime comparison for circuits whose initial mapping was combinational  | 69  |

| 2.3 | Runtime comparison for circuits whose initial mapping was not combi-     |     |

|     | national                                                                 | 69  |

| 2.4 | Results for randomly generated functions of five variables               | 70  |

| 3.1 | Results of the forward-search method on the table3 benchmark. Each       |     |

|     | function is a PO expressed in terms of the PIs and other POs             | 92  |

| 3.2 | Results of the backward-search method on the table3 benchmark. Each      |     |

|     | function is a PO expressed in terms of the PIs and other POs             | 92  |

| 3.3 | A table of the averaged results using the forward-search method among    |     |

|     | different benchmarks.                                                    | 93  |

| 3.4 | A table of the averaged results using the backward-search method among   |     |

|     | different benchmarks.                                                    | 93  |

| 4.1 | Results of Steps 1 through 4 of our algorithm applied to a set of bench- |     |

|     | marks. The timeout was set to 200 seconds                                | 106 |

| 5.1 | Results of running the state cube and gate cube implementations on       |     |

|     | satisfiable benchmarks                                                   | 128 |

| 5.2 | Results of running the state cube and gate cube implementations on       |     |

|     | unsatisfiable benchmarks                                                 | 131 |

# List of Figures

| 1.1 | A diagram of how the thesis topics relate to each other                           | 2  |

|-----|-----------------------------------------------------------------------------------|----|

| 1.2 | Variables for deciding what bar to go to for happy hour                           | 3  |

| 1.3 | Constraints for deciding what bar to go to for happy hour $\ldots \ldots \ldots$  | 4  |

| 1.4 | Nand Template for Tseitin transformation                                          | 7  |

| 1.5 | A circuit implementing function $f = ab + \overline{cd}$                          | 8  |

| 1.6 | The circuit in Figure 1.5 expressed in terms of AND gates and inverters.          |    |

|     | The Tseitin transformation using the template from Figure 1.4 is shown            |    |

|     | beneath the circuit. The table on the right side of the Figure lists all the      |    |

|     | satisfying assignments of the SAT instance.                                       | 8  |

| 2.1 | Example: A cyclic circuit with 4 primary inputs and 3 primary outputs.            | 11 |

| 2.2 | Network in Figure 2.1 with $a = 1, b = 0, c = 1, d = 0.$                          | 12 |

| 2.3 | Network in Figure 2.1 with $a = 1, b = 1, c = 0, d = 0.$                          | 12 |

| 2.4 | A cyclic combinational circuit.                                                   | 13 |

| 2.5 | Three four-input lookup tables implement functions $f = ab \oplus cde$ and        |    |

|     | $g=ab\bar{c}\oplus de$ using an acyclic topology. The circuit's dependency graph  |    |

|     | is shown on the right.                                                            | 16 |

| 2.6 | Two four-input lookup tables implement functions $f = ab \oplus cde$ and          |    |

|     | $g=ab\bar{c}\oplus de$ using a cyclic topology. The circuit's dependency graph is |    |

|     | shown on the right                                                                | 17 |

| 2.7 | An AND gate with 0, 1, and $\perp$ inputs                                         | 18 |

| 2.8  | An illustration unknown/undefined values $\perp$                                                  | 18 |

|------|---------------------------------------------------------------------------------------------------|----|

| 2.9  | A cyclic circuit that is not combinational. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 20 |

| 2.10 | The circuit of Figure 2.9 with $x_1 = 1$ , $x_2 = 0$ and $x_3 = 1$                                | 20 |

| 2.11 | Analysis of the circuit in Figure 2.9.                                                            | 20 |

| 2.12 | The function $ab + c\bar{b}$ and a gate level implementation                                      | 21 |

| 2.13 | Four different implementations of two functions, $f_1$ and $f_2$ , of five vari-                  |    |

|      | ables $a, b, c, d$ , and $x$                                                                      | 24 |

| 2.14 | Functions $f_1(a, b, x, f_2)$ and $f_2(c, d, x, f_1)$ with $x = 0$ and $x = 1$ . For both         |    |

|      | values of $x$ , the dependency graphs become acyclic                                              | 25 |

| 2.15 | A miter that checks to see if $f_0$ can be specified in terms of $f_1$ , $f_2$ , and $f_3$ .      | 27 |

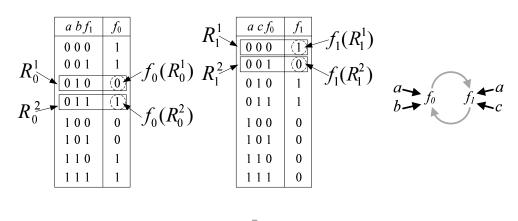

| 2.16 | The truth tables for two functions. The cyclic dependency graph con-                              |    |

|      | taining these two functions is not combinational. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 29 |

| 2.17 | The dependency graph for the functions in Figure 5.3 for the assignment:                          |    |

|      | a = c = 0, b = 1. The dependency graph is not combinational                                       | 30 |

| 2.18 | The truth tables for two functions. The cyclic dependency graph contain-                          |    |

|      | ing these two functions is not combinational. This figure also illustrates                        |    |

|      | a specific selection of rows that proves that the cyclic dependency graph                         |    |

|      | is not combinational                                                                              | 31 |

| 2.19 | A SAT instance that verifies whether or not the functions described in                            |    |

|      | Figure 5.3 are combinational                                                                      | 32 |

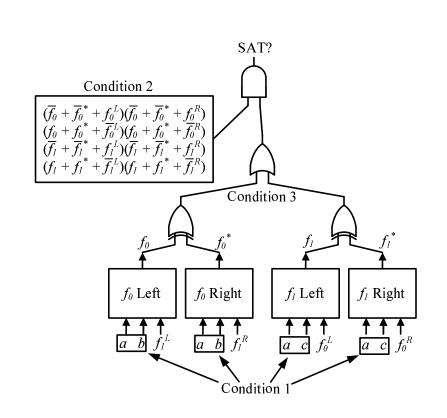

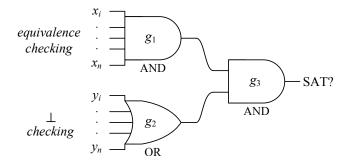

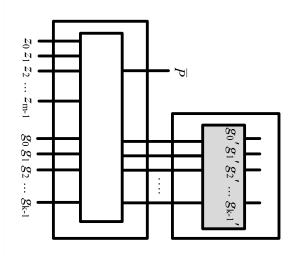

| 2.20 | A SAT instance that checks if the set of functions $F = \{f_0, f_1, \dots, f_{n-1}\}$             |    |

|      | of variables $X = \{x_0, x_1, \dots, x_{m-1} \text{ is combinational. } \dots \dots$              | 35 |

| 2.21 | Pseudocode for our synthesis algorithm. Magnitude symbols $( magnitude )$  |    |

|------|----------------------------------------------------------------------------|----|

|      | are used to indicate the size of a list. The subscript $i$ , when applied  |    |

|      | to a list, indicates an access to the $i$ -th element of the list. The de- |    |

|      | pendency graph variables (e.g., DepGraph, DepGraphCopy, and Small-         |    |

|      | estDepGraph) are lists of support sets for each function. The routine      |    |

|      | "SmallestSupportSet" returns the smallest support set for a particular     |    |

|      | function from a list of support sets. The routine "NextSmallestSupport-    |    |

|      | Set" returns the next smallest support set from a list of support sets for |    |

|      | a particular function. The routine "SupportSetSize" returns the sum of     |    |

|      | the size of all the support sets for a given dependency graph. The routine |    |

|      | "DepGraphIsCombinational" performs the SAT-based analysis described        |    |

|      | in the previous section; it returns $True$ if the dependency graph is com- |    |

|      | binational. The routine "FunctionIsNotCombinational" returns $True$ if     |    |

|      | there is a primary input assignment that causes the given function to      |    |

|      | evaluate to $\perp$                                                        | 38 |

| 2.22 | An illustration of the synthesis algorithm on an example consisting of     |    |

|      | 3 functions and 4 primary input variables. The thin gray arrows indi-      |    |

|      | cate cyclic dependencies in the dependency graphs. Some branches are       |    |

|      | omitted for clarity, as indicated by ""                                    | 39 |

| 2.23 | The two functions "SupportSets" and "SupportSetsHelper" are used to                        |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | generate a list of valid support sets for a target function. The function                  |    |

|      | "PossibleSupportVars" returns a list of variables that could possibly be                   |    |

|      | used as a support variable for the target function. The "SupportSets"                      |    |

|      | function initializes the list of support sets and the list of possible support             |    |

|      | set variables before calling the "SupportSetsHelper" function. The "Sup-                   |    |

|      | portSetsHelper" function checks to see if the set of current variables is a                |    |

|      | superset of some already found support set. If it is not, the SAT based                    |    |

|      | check discussed in Section $2.3.1$ is performed to determine if the current                |    |

|      | set of variables can be used to represent the target function. If they can,                |    |

|      | then the function is called recursively with each variable removed once                    |    |

|      | from the set of current support variables. If none of these support sets                   |    |

|      | can be used to represent the target function, then this indicates that no                  |    |

|      | subset of the current support set variables can be used to represent the                   |    |

|      | target function. In this case, the current set of support variables is added               |    |

|      | to the list of support sets                                                                | 41 |

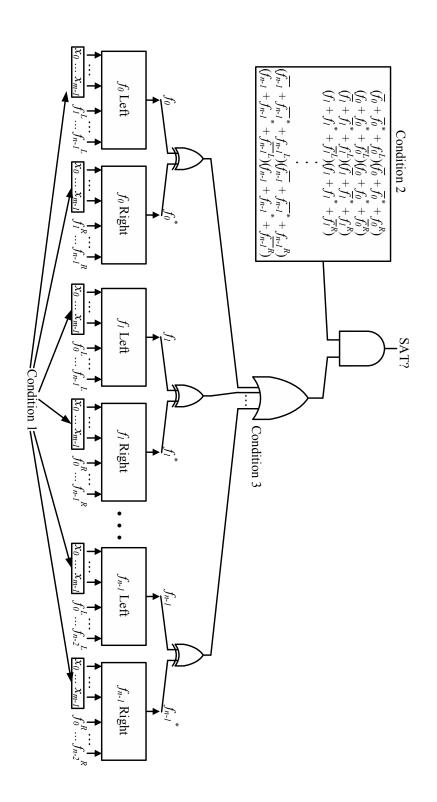

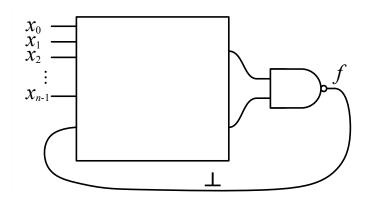

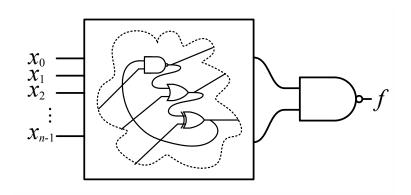

| 2.24 | An illustration of how SAT-based analysis works. If the circuit is combi-                  |    |

|      | national, the SAT solver returns an answer of $UNSAT$ . If the circuit is not              |    |

|      | combinational, it returns an answer of $S\!AT$ and it provides a satisfying                |    |

|      | assignment.                                                                                | 46 |

| 2.25 | Dual-rail encoding scheme for ternary values. The left two columns show                    |    |

|      | the value for each wire in the dual-rail encoding, and the right most                      |    |

|      | column shows the corresponding ternary value. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 48 |

| 2.26 | Constructing the SAT instance                                                              | 50 |

| 2.27 | A cyclic circuit                                                                           | 51 |

| 2.28 | The circuit in Figure 2.27 with cycles broken.                                             | 51 |

| 2.29 | The SAT circuit corresponding to the cyclic circuit in Figure 2.27                         | 52 |

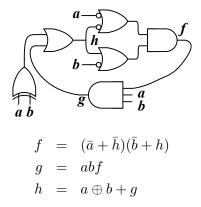

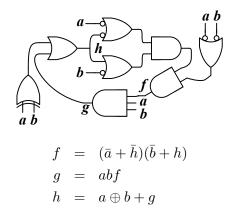

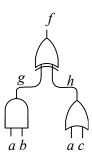

| 2.30 | A cyclic specification of three Boolean functions, $f, g$ and $h$ . These                                                              |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|      | evaluate to definite Boolean values for all assignments of the inputs $a$                                                              |    |

|      | and $b$                                                                                                                                | 55 |

| 2.31 | Individual gate mappings for the functions in Figure 2.30                                                                              | 55 |

| 2.32 | The circuit obtained by assembling the mappings in Figure 2.31 together.                                                               |    |

|      | It is <i>not</i> combinational                                                                                                         | 56 |

| 2.33 | The circuit in Figure 2.32 with additional logic. It is combinational. $\ .$ .                                                         | 56 |

| 2.34 | Example 4: A mapping fix without a product covering assignment $a =$                                                                   |    |

|      | $b = d = 1, c = e = \perp \dots \dots$ | 62 |

| 2.35 | Example 5: A mapping fix that works                                                                                                    | 63 |

| 2.36 | The incorrect fix in Example 4. The function $f$ is not controlled for this                                                            |    |

|      | assignment of $a$ and $c$ .                                                                                                            | 64 |

| 2.37 | The correct fix Example 5. The function $f$ assumes the correct value of                                                               |    |

|      | 1 when $a$ is 0                                                                                                                        | 64 |

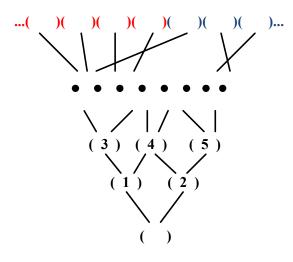

| 3.1  | A resolution proof from an unsatisfiable CNF formula. Clauses of $\boldsymbol{A}$ are                                                  |    |

|      | shown in red while clauses of $B$ are shown in blue $\ldots \ldots \ldots \ldots$                                                      | 72 |

| 3.2  | A different resolution proof from the same unsatisfiable CNF formula.                                                                  |    |

|      | Clauses of $\boldsymbol{A}$ are shown in red while clauses of $\boldsymbol{B}$ are shown in blue $\ . \ .$                             | 72 |

| 3.3  | The DPLL algorithm. The "propagate<br>( $l,\sigma)$ " function assigns "TRUE" to                                                       |    |

|      | every instance of $l$ in $\sigma$ . The "var-decision( $\sigma$ )" function decides a truth                                            |    |

|      | value for an unassigned variable and returns the corresponding literal.                                                                | 74 |

| 3.4  | A CNF formula of variables $w, x, y$ , and $z$                                                                                         | 75 |

| 3.5  | The CNF formula shown in Figure 3.4 with additional learned clauses                                                                    |    |

|      | (y+z) and $(z)$                                                                                                                        | 76 |

| 3.6  | A CNF formula from Figure 3.4 with assumption variables $a_1, a_2, a_3, a_4$ ,                                                         |    |

|      | $a_5$                                                                                                                                  | 77 |

| 3.7  | A CNF formula from Figure 3.6 with two additional learned clauses $\ . \ .$                                                            | 77 |

| 3.8  | A resolution proof of unsatisfiability                                                                                                 | 78 |

| 3.9  | The algorithm proposed in [1] to produce a circuit that implements an                                |     |

|------|------------------------------------------------------------------------------------------------------|-----|

|      | interpolant of a given clause partition, via a proof of unsatisfiability. $\ .$ .                    | 79  |

| 3.10 | Two interpolants produced by calling $\mathbf{p}(c)$ on the empty clause of a res-                   |     |

|      | olution proof. The circuits on the left and right are generated from the                             |     |

|      | proofs in Figures 3.1 and 3.2, respectively                                                          | 80  |

| 3.11 | A resolution proof from an unsatisfiable CNF formula. Clauses of $\boldsymbol{A}$ are                |     |

|      | shown in red while clauses of $\boldsymbol{B}$ are shown in blue. Nodes 1, 2, 3, 4, and              |     |

|      | 5 are nodes somewhere in the proof                                                                   | 86  |

| 3.12 | A circuit with an observability don't care of $g = 1, h = 0$                                         | 94  |

| 4.1  | A conceptual example of two resolution proofs with very few shared                                   |     |

|      | clauses. The resulting interpolants do not contain any shared logic                                  | 98  |

| 4.2  | An conceptual example of two resolution proofs that share many of the                                |     |

|      | same clauses. The resulting interpolants share some of same logic. $\ . \ .$                         | 98  |

| 4.3  | A SAT instance that checks the existence of target function $g_i$ with sup-                          |     |

|      | port set $x_0, x_1, \ldots, x_n$ .                                                                   | 100 |

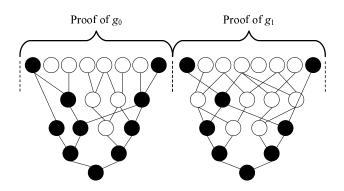

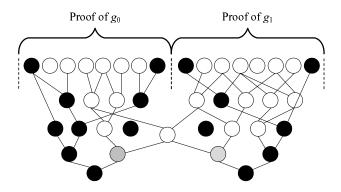

| 4.4  | Two resolution proofs without any shared nodes                                                       | 102 |

| 4.5  | Two resolution proofs with a shared node. An additional white node is                                |     |

|      | added to the proof, but two black nodes can then be removed. The gray                                |     |

|      | nodes are nodes that were black but can now be colored white. $\ldots$ .                             | 102 |

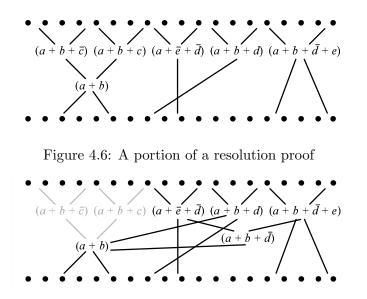

| 4.6  | A portion of a resolution proof $\ldots$                                                             | 104 |

| 4.7  | A portion of a resolution proof that has been restructured. Clause $(a+b)$                           |     |

|      | can be resolved from clauses $(a + \bar{e} + \bar{d})$ , $(a + b + d)$ and $(a + b + \bar{d} + e)$ . |     |

|      | Restructuring the proof this way adds one clause and removes two others.                             | 104 |

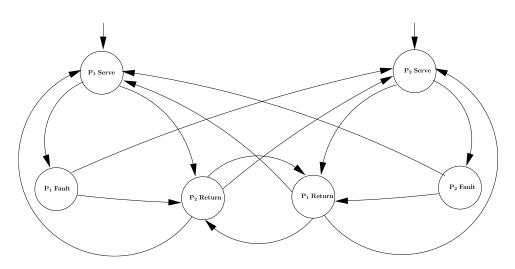

| 5.1  | A state transition graph of a two player game of racquetball.                                        | 110 |

| 5.2 | Pseudocode for the interpolation-based model checking algorithm given                     |     |

|-----|-------------------------------------------------------------------------------------------|-----|

|     | by McMillan [1]. Lines beginning with an asterisk $(\ast)$ indicate comments.             |     |

|     | The function "interpolant $(A, B)$ " returns an interpolant $R'$ such that                |     |

|     | $A \to R'$ and $R' \to \neg B$ . The algorithm returns <i>true</i> if the property holds, |     |

|     | $false$ if the property fails, and $maybe\ false$ if the property might fail              |     |

|     | (the counter example might be spurious). $\ldots \ldots \ldots \ldots \ldots \ldots$      | 116 |

| 5.3 | An example netlist where fewer cubes in terms of intermediate variables                   |     |

|     | need to be blocked than cubes in terms of state variables                                 | 120 |

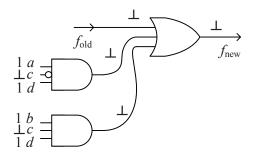

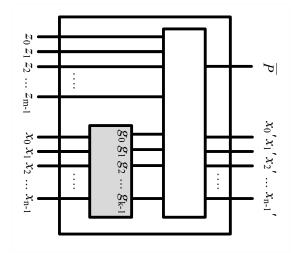

| 5.4 | A transition relation that is used in a frame for the standard PDR im-                    |     |

|     | plementation                                                                              | 121 |

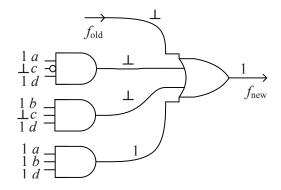

| 5.5 | A transition relation that is used for blocking cubes of gate variables                   | 123 |

| 5.6 | An example used to illustrate subtleties when using ternary valued sim-                   |     |

|     | ulation on cubes of gate variables                                                        | 125 |

| 6.1 | A cyclic combinational circuit that must be larger than some equivalent                   |     |

|     | acyclic circuit                                                                           | 134 |

| 6.2 | A cyclic combinational circuit that might be smaller than all equivalent                  |     |

|     | acyclic circuits.                                                                         | 134 |

|     |                                                                                           |     |

### Chapter 1

## Overview

This first chapter serves as an introduction to concepts and terms that are common to all the topics presented in this dissertation. We begin by discussing the organization and how the subjects are related.

#### **1.1** Organization and Contributions

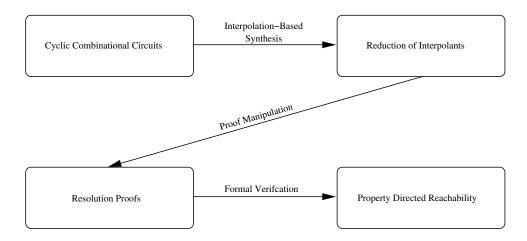

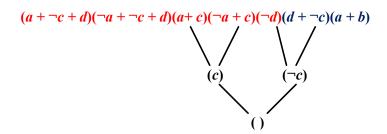

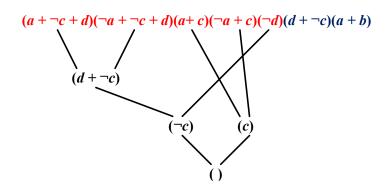

This thesis encompasses many of the topics that I researched during my graduate education. Each of these topics naturally evolved out of the previous while maintaining the common theme of Boolean Satisfiability. The topics in this thesis are presented in the order in which preserves this natural evolution. Figure 1.1 shows how the topics relate to each other. The first topic discusses how to analyze and synthesize cyclic combinational circuits with Boolean Satisfiability. The synthesis method relies on generating Craig Interpolants to generate functional dependencies. The second topic, Reduction of Interpolants for Logic Synthesis, discusses a method for reducing the size of these interpolants. This method modifies the structure of resolution proofs to reduce the complexity of the interpolant's structure. The third topic discusses how resolution proofs can be used as an underlying data structure in which to perform synthesis. Resolution proofs and Craig Interpolants are common constructs used in formal verification. The final topic of this thesis discusses some improvements to a new SAT-based algorithm for formally verifying safety properties in a finite-state transition system.

Figure 1.1: A diagram of how the thesis topics relate to each other.

Explicitly stated, this thesis makes the following contributions:

- We propose a SAT-Based algorithm to analyze and synthesize cyclic combinational circuits on a network level. This method synthesizes cyclic circuits while trying to minimize the support set size of the circuit's intermediate functions.

- We propose a SAT-Based algorithm for analyzing and mapping cyclic circuits with gate-level implementations. There are subtle challenges associated with translating cyclic circuits from a network-level to a gate-level implementation that we address.

- We propose a method for reducing the size of Craig Interpolants used to synthesize functional dependencies.

- We discuss the use of resolution proofs as a general data structure for logic synthesis.

• We discuss some improvements to a new model checking algorithm known as Property Directed Reachability.

In the following section we describe concepts and notation that are common to most of the concepts in this thesis.

#### 1.2 Definitions, Notation, and Common Concepts

#### 1.2.1 Boolean Satisfiability

Boolean satisfiability is the problem of determining whether there exists some truth assignment to the variables of a Boolean formula such that the formula is satisfied (is true for that assignment). Many combinatorial problems can be described simply by a set of Boolean constraints. Thus many combinatorial problems are easily translated into the Boolean Satisfiability problem. For example, consider the problem of three Ph.D. students (Hua, John, and Mustafa) deciding where to go to happy hour. This problem consists of a number of variables and constraints. The variables and their meanings are listed in Figure 1.2. The constraints and their meanings are listed in Figure 1.3.

| Variable   | Meaning                                            |

|------------|----------------------------------------------------|

| Joh_Att    | John will attend                                   |

| $Mus\_Att$ | Mustafa will attend                                |

| $Hua\_Att$ | Hua will attend                                    |

| $Hua\_Dea$ | Hua has a paper deadline he needs to meet          |

| $Mus\_Per$ | Mustafa has permission to go from his wife Banu    |

| $Gro_Mee$  | There is a group meeting scheduled for the evening |

| $War_Wea$  | The weather is warm                                |

| $Bur\_Loc$ | The students will go to the bar: "Burrito Loco"    |

| $Stu\_Her$ | The students will go to the bar: "Stub & Herbs"    |

| Sal        | The students will go to the bar: "Sally's"         |

Figure 1.2: Variables for deciding what bar to go to for happy hour.

The truth assignments to the Boolean variables listed in Figure 1.2 that satisfy all of the constraints in Figure 1.3 represent the possible scenarios in which at least some

| Constraint                                               | Meaning                                        |  |  |  |

|----------------------------------------------------------|------------------------------------------------|--|--|--|

| $Joh_Att \rightarrow Hua_Att \lor Mus_Att$               | A student will only attend if at least         |  |  |  |

| $Hua\_Att \rightarrow Joh\_Att \lor Mus\_Att$            | one of the other students attends              |  |  |  |

| $Mus\_Att \rightarrow Hua\_Att \lor Joh\_Att$            |                                                |  |  |  |

| $Mus\_Att \rightarrow Mus\_per \land \neg Gro\_Mee$      | Mustafa will attend only if he has permission  |  |  |  |

|                                                          | and there is no group meeting                  |  |  |  |

| $Hua\_Att \rightarrow \neg Hua\_Dea \land \neg Gro\_Mee$ | Hua will attend only if he does not have       |  |  |  |

|                                                          | a paper deadline and there is no group meeting |  |  |  |

| $Bur\_Loc \rightarrow \neg Hua\_Att$                     | Hua refuses to go to "Burrito Loco"            |  |  |  |

| $Stu\_Her \rightarrow \neg War\_Wea$                     | The students will only go to "Stub and Herbs"  |  |  |  |

|                                                          | if the weather is not warm                     |  |  |  |

| $Sal \rightarrow War_Wea \lor \neg Joh_Att$              | John refuses to go to "Sally's"                |  |  |  |

|                                                          | unless the weather is warm                     |  |  |  |

| $Bur\_Loc \rightarrow \neg Sal \land \neg Stu\_Her$      | The students cannot attend more than one bar   |  |  |  |

| $Stu\_Her \rightarrow \neg Sal \land \neg Bur\_Loc$      |                                                |  |  |  |

| $Sal \rightarrow \neg Bur\_Loc \land \neg Stu\_Her$      |                                                |  |  |  |

| $Joh\_Att \lor Hua\_Att \lor Mus\_Att$                   | At least one student will attend               |  |  |  |

Figure 1.3: Constraints for deciding what bar to go to for happy hour

of the students will attend happy hour. For example, the truth assignment:  $Joh_Att = Hua_Att = Mus_Att = War_Wea = Mus_Per = Sal = true, Hua_Dea = Bur_Loc = Stu_Her = Gro_Mee = false satisfies all of the constraints. This indicates a scenario where all of the students attend "Sally's". Another satisfying assignment: <math>Joh_Att = Mus_Att = Hua_Dea = Mus_Per = Stu_Her = true, Hua_Att = Bur_Loc = Sal = Gro_Mee = false indicates a scenario where only John and Mustafa go to "Stub & Herbs" because Hua has a paper deadline. Notice that in this scenario the truth value of the variable <math>War_Wea$  does not affect the truth values of the constraints. There are several truth values which do not satisfy all of the constraints. For example, whenever there is a group meeting, neither Mustafa nor Hua will be able to go out for happy hour. Because neither Hua nor Mustafa will attend happy hour, John will also not attend (though he doesn't seem to care about the group meeting...). In fact, it can be shown through repeated use of the inference rule of resolution that the constraint:  $Gro_Mee \to \neg(Joh_Att \lor Hua_Att \lor Mus_Att)$  can be implied by the conjunction of

constraints in Figure 1.3. This means that the final constraint: "At least one student will attend." cannot be satisfied when there is a group meeting scheduled.

For the majority of this thesis, we use the "Electrical Engineering" notation: addition (x + y) denotes disjunction, multiplication (xy), denotes conjunction, a "plus with a circle"  $(x \oplus y)$  denotes inequivalence (exclusive OR), and an overbar  $(\bar{x})$  or a "dash with a tail"  $(\neg x)$  denotes negation. However, in the example above, in the final chapter, and in some pseudocode, we use the standard mathematical notation: a " $\lor$ " denotes disjunction, a " $\land$ " denotes conjunction, and a " $\rightarrow$ " denotes implication. We often use the number 1 to indicate the constant **true** and the number 0 to indicate the constant **false**; although we sometimes explicitly say "true" or "false". We use the term "Boolean formula" and "Boolean function" interchangbly. If we are discussing a function that is not Boolean (either its arguments are not Boolean or its result is not Boolean) it will be made clear by context.

An appearance of a variable in a Boolean formula, either negated or non-negated, is referred to as a **literal**. A **clause** or a **sum** is a disjunction (OR) of literals. A conjunction (AND) of literals is referred to as a **cube** or a **product**. A Boolean formula is in conjunctive normal form (CNF) if it is a conjunction (AND) of clauses. We will sometimes refer to a CNF formula as a set of clauses, when it is clear by context. The vast majority of SAT solvers only operate on CNF formulas. Though there are some that operate on circuit structures, or a combination of circuit structures and CNF formulas [2]. Any representation of a Boolean formula can be transformed into a CNF formula that preserves the satisfiability of the original in linear time by adding additional variables and constraints. The most common type of transformation, introduced by Tseitin in [3], is described in subsection 1.2.2.

A CNF formula is said to be **satisfiable** if there is some assignment of its variables that causes the formula to evaluate to true. A CNF formula is said to be **unsatisfiable** if there is no assignment of its variables that causes the formula to evaluate to true. We sometimes refer to a CNF formula as a **SAT Instance**. We will also refer to a logic circuit with a single primary output as a SAT instance; the satisfiability of the primary output can be represented as a CNF formula.

The **restriction** operation (also known as the cofactor) of a function f with respect to a variable x,

$$f|_{x=v},$$

refers to the assignment of the constant value  $v \in \{0,1\}$  to x. A function f depends upon a variable x iff  $f|_{x=0}$  is not identically equal to  $f|_{x=1}$ . Call the variables that a function depends upon its support set.

We use superscripts to denote a function's ON and OFF sets: for a function  $f(x_0, x_1, \ldots, x_n)$ , we write  $f(x_0, x_1, \ldots, x_n)^1$  to denote its ON set (i.e., the set of assignments to variables  $x_0, x_1, \ldots, x_n$  where f evaluates to 1); we write  $f(x_0, x_1, \ldots, x_n)^0$  to denote its OFF set (i.e., the set of assignments to variables  $x_0, x_1, \ldots, x_n$  where f evaluates to 0).

A **partial assignment** of a function's support variables is a valuation of that function over a subset of its support variables; the result of a partial assignment is either 0, 1, or  $\perp$  (the definition of  $\perp$  is described in Chapter 2). A product is said to **cover** a partial assignment if that product evaluates to 1 for that partial assignment. Similarly, a sum is said to cover a partial assignment if the sum evaluates to 0 for that partial assignment.

When we assert some implication or bi implication in the text, we are claiming that the implication or bi implication is a tautology. For example, if we say something like "the cube c is true because  $f \to a$  and  $a \leftrightarrow c$ ", then we are asserting that  $f \to a$  and  $a \leftrightarrow c$  are both tautologies.

Given a product p and a function f, we say that "p is a product of f" if  $p \to f$ . Likewise, given a sum s and a function f, we say that "s is a sum of f" if  $f \to s$ .

A **prime implicant** p of some function f is a product such that  $p \to f$  and p is not covered by any other product q of f ( $p \not\to q$ ). A **prime implicate** s of some function f is a sum such that  $f \to s$  and s is not covered by any other sum q of f ( $q \not\to s$ ) [4].

#### 1.2.2 Tsestin Transformation

In order for CNF-based SAT Solvers to reason about circuit structures, a translation from a combinational circuit to an equivalent CNF formula must take place. The most common, and arguably the most simple, type of translation was introduced by Tsetien [3].

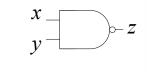

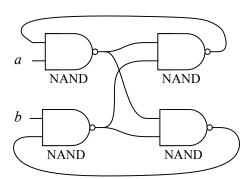

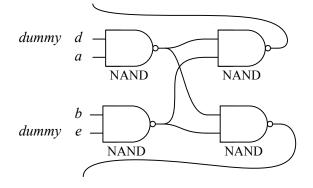

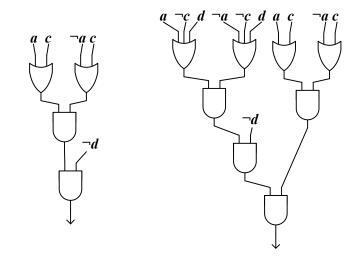

The transformation generates a CNF formula such that the number of clauses and variables are linear in the size of the circuit. The translation works be converting each individual logic gate into a set of clauses. These clauses are in terms of variables assigned to each wire connecting to the logic gate. An example template for a NAND gate is shown in Figure 1.4

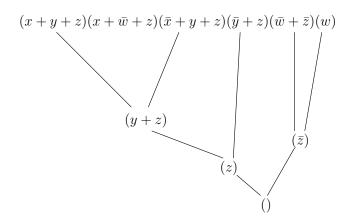

$(x+z)(y+z)(\bar{x}+\bar{y}+\bar{z})$

Figure 1.4: Nand Template for Tseitin transformation

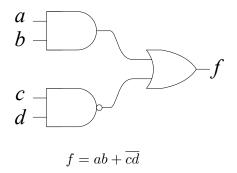

While the original circuit expresses a Boolean function in terms a set of primary input variables, the transformed CNF formula is expressed in terms of not only the primary input variables but also variables representing the state of each individual wire in the circuit. Assignments that satisfy the final formula correspond to **valid states** of the circuit. For example, consider the circuit and corresponding formula shown in Figure 1.5.

Using Demorgan's law, the OR gate can be converted into an AND gate with inverters on every input and output. Applying Demorgan's law, simplifying multiple inversions, and applying the template given in Figure 1.4 yields the circuit and corresponding Tseitin transformation shown in Figure 1.6

Figure 1.5: A circuit implementing function  $f = ab + \overline{cd}$ .

|                                             | Satisfiable Assignments |                     |        |                     |

|---------------------------------------------|-------------------------|---------------------|--------|---------------------|

|                                             | a,b,c,d                 | $x = \overline{ab}$ | y = cd | $f = \overline{xy}$ |

|                                             | 0000                    | 1                   | 0      | 1                   |

|                                             | $0 \ 0 \ 0 \ 1$         | 1                   | 0      | 1                   |

| $b$ $\rightarrow$                           | $0\ 0\ 1\ 0$            | 1                   | 0      | 1                   |

|                                             | $0\ 0\ 1\ 1$            | 1                   | 1      | 0                   |

| $\frown$                                    | $0\ 1\ 0\ 0$            | 1                   | 0      | 1                   |

|                                             | $0\ 1\ 0\ 1$            | 1                   | 0      | 1                   |

|                                             | $0\ 1\ 1\ 0$            | 1                   | 0      | 1                   |

|                                             | $0\ 1\ 1\ 1$            | 1                   | 1      | 0                   |

|                                             | $1 \ 0 \ 0 \ 0$         | 1                   | 0      | 1                   |

| $(a+x)(b+x)(\bar{a}+\bar{b}+\bar{x})$       | $1 \ 0 \ 0 \ 1$         | 1                   | 0      | 1                   |

|                                             | $1 \ 0 \ 1 \ 0$         | 1                   | 0      | 1                   |

| $(c+\bar{y})(d+\bar{y})(\bar{c}+\bar{d}+y)$ | $1 \ 0 \ 1 \ 1$         | 1                   | 1      | 0                   |

| $(x+f)(y+f)(\bar{x}+\bar{y}+\bar{f})$       | $1 \ 1 \ 0 \ 0$         | 0                   | 0      | 1                   |

|                                             | $1 \ 1 \ 0 \ 1$         | 0                   | 0      | 1                   |

|                                             | $1\ 1\ 1\ 0$            | 0                   | 0      | 1                   |

|                                             | $1\ 1\ 1\ 1\ 1$         | 0                   | 1      | 1                   |

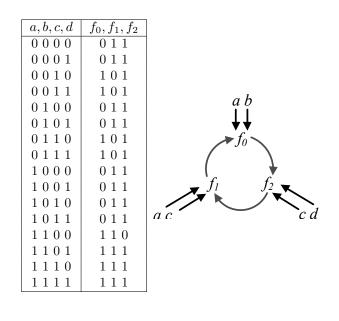

Figure 1.6: The circuit in Figure 1.5 expressed in terms of AND gates and inverters. The Tseitin transformation using the template from Figure 1.4 is shown beneath the circuit. The table on the right side of the Figure lists all the satisfying assignments of the SAT instance.

There are 16 valid states of the circuit in Figure 1.5. Hence there are only 16 assignments that satisfy the clauses in Figure 1.6. These assignments are explicitly listed on the right hand side of the Figure. It may be somewhat counterintuitive that the assignments that satisfy the SAT instance in Figure 1.6 do not neccessarily correspond to those that cause the primary output variable f to evaluate to 1. In order to check the satisfiability of the circuit in Figure 1.5, the clause containing the single variable f can be added to the SAT instance in Figure 1.6 to assert that f must be 1 in order to satisfying the formula.

## Chapter 2

# Cyclic Circuits and Boolean Satisfiability

#### 2.1 Introduction

#### 2.1.1 Cyclic Combinational Circuits

A common misconception is that combinational circuits must have *acyclic* topologies; that is to say, they must be designed without any loops or feedback paths. Indeed, any acyclic circuit is clearly combinational: once the current values of the inputs are set, the signals propagate to the outputs; the outputs are determined regardless of the prior values on the wires, making them independent of the past sequence of inputs. The idea that "combinational" and "acyclic" are synonymous terms is so thoroughly ingrained that many textbooks provide the latter as a definition of the former (e.g., [5], p. 14; [6], p. 193).

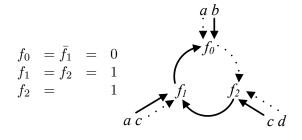

And yet, cyclic circuits can be combinational. Consider the truth table of values and the functions shown in Figure 2.1. The definition of these functions is cyclic. In spite of this, the network is combinational: it produces the correct outputs, regardless of the initial state and independently of all timing assumptions. To see this, consider specific input values. For instance, with a = 1, b = 0, c = 1, d = 0, the network simplifies to that shown in Figure 2.2, yielding the correct values for  $f_0, f_1$  and  $f_2$ . With a = 1, b = 1, c = 0, d = 0, the network simplifies to that shown in Figure 2.3, again yielding the correct values for  $f_0, f_1$  and  $f_2$ . The reader may verify that the network implements the correct output values for all input values.

$$f_0 = ab + f_1$$

$$f_1 = \bar{c} + f_2 a$$

$$f_2 = c + d + \bar{f}_0$$

Figure 2.1: Example: A cyclic circuit with 4 primary inputs and 3 primary outputs.

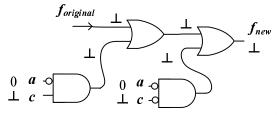

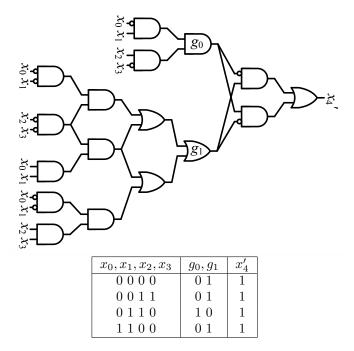

Cyclic circuits can be analyzed on a network level, such as the example in Figure 2.1, or on the level of logic gates mapped to some technology. A cyclic combinational circuit mapped to two-input AND and OR gates is shown in Figure 2.4. This circuit is also combinational in the strictest sense: it produces the required output values *regardless*

Figure 2.2: Network in Figure 2.1 with a = 1, b = 0, c = 1, d = 0.

Figure 2.3: Network in Figure 2.1 with a = 1, b = 1, c = 0, d = 0.

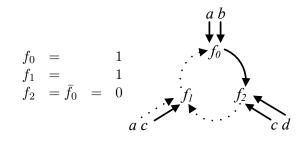

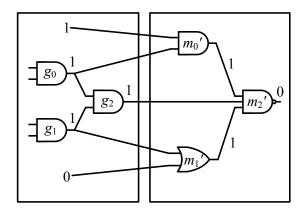

of the prior values on the wires and for any choice of delay parameters. If x = 0 then  $g_1$  produces an output of 0, because 0 is a controlling value for an AND gate. If x = 1 then  $g_4$  produces a value of 1, because 1 is a controlling value for an OR gate. In both cases, the cycle is broken and the circuit produces definite outputs. Since x must assume one of these two values, we conclude that the circuit always produces definite outputs. In fact, it implements two functions that both depend on all five variables:

$$f_1 = b(a + x(d + c)),$$

$$f_2 = d + c(x + b a)$$

(4) denotes OR, (·) denotes AND

(5)

Note that the computation of the two functions overlaps. If we were to implement these functions with an acyclic circuit, we would need eight two-input gates. There can be subtle differences between the behavior of a cyclic circuit defined on the network-level and it's gate-level implementation. We discuss these differences towards the end of this chapter.

Figure 2.4: A cyclic combinational circuit.

The concept of cycles in combinational circuitry is conceptually similar to that of *false paths*. Khrapchenko was the first to recognize that *depth* and *delay* in a circuit are not equivalent concepts: the critical paths of a circuit may all be false, i.e., they might be blocked by off-path controlling values; as a consequence, the delay of the circuit might be less than its topological depth [7]. For a cyclic circuit, we can say that it is combinational if all of its cycles are false; no input assignment ever causes a cyclic path to be sensitized. Although counterintuitive, cycles can be used to optimize circuits for delay as well as for area. The extra flexibility of allowing cycles when structuring functional dependencies makes it possible to move logic off of true critical paths and so optimize the delay [8].

In previous work, it was shown that combinational circuits can be optimized significantly if cycles are introduced [9]. The intuition behind this is that, with feedback, all nodes can potentially benefit from work done elsewhere; without feedback, nodes at the top of the hierarchy must be constructed from scratch. The proposed methodology for synthesizing such circuits demonstrated that significant improvements in area and in delay could be. Cycles are introduced in the restructuring and minimization phases of logic synthesis at the level of functional dependencies.

#### 2.1.2 Prior and Related Work

In an earlier era, theoreticians commented on the possibility of having cycles in combinational logic and conjectured that this might be a useful property [10], [11], [12]. Both McCaw and Rivest presented examples of cyclic circuits with provably fewer gates than is possible with equivalent acyclic circuits [13], [14].

Stok lamented that EDA tools were rejecting cyclic designs because there was no way to validate them [15]. In response, Malik discussed analysis techniques for cyclic combinational circuits [16]. His approach was topological, beginning with a transformation from a cyclic specification to an equivalent acyclic one. Later Shiple refined and formalized Malik's results and extended the concepts to combinational logic embedded in sequential circuits [17].

More recently, Neiroukh and Edwards discussed analysis strategies targeting cyclic circuits that are produced inadvertently during design [18, 19]. Following a strategy similar to Malik's, they proposed techniques for transforming valid cyclic circuits into functionally equivalent acyclic circuits [19]. Their algorithm enumerates partial Boolean assignments that break the feedback paths in cyclic circuits. The enumeration continues until enough assignments are found to cover the entire input space. Based on these partial assignments, acyclic fragments are assembled into a new acyclic circuit. As a starting point, they presume that the given circuit is combinational and correctly mapped. The enumeration is explicit and so the algorithm is potentially very slow, as it searches through an exponentially large space of partial assignments.

Riedel was the first to suggest a method for synthesizing cyclic circuits [9]. The method was implemented in a package called CYCLIFY, built within the Berkeley SIS environment [20]. The tool was successful: it reduced the area of benchmark circuits by as much as 30% and the delay by as much as 25%. However, being based on SIS, the analysis routines in CYCLIFY used sum-of-products (SOP) and binary decision diagram (BDD) representations for Boolean functions. These representations limited the size of the circuits that could be analyzed and optimized effectively.

Admittedly, the task of analyzing cyclic circuits is complex. Yet there is no fundamental obstacle to performing tasks such as verification, mapping, and timing analysis on cyclic circuits. So-called "false-path aware" algorithms for timing analysis take into account false paths, providing tighter bounds on delay than purely topological methods [21]. The complexity of this sort of timing analysis is, in fact, the same for cyclic circuits as for acyclic circuits [22]. Early formulations based on SOPs and BDDs were never up to the task, but modern SAT-based algorithms are powerful enough to perform false-path aware analysis.

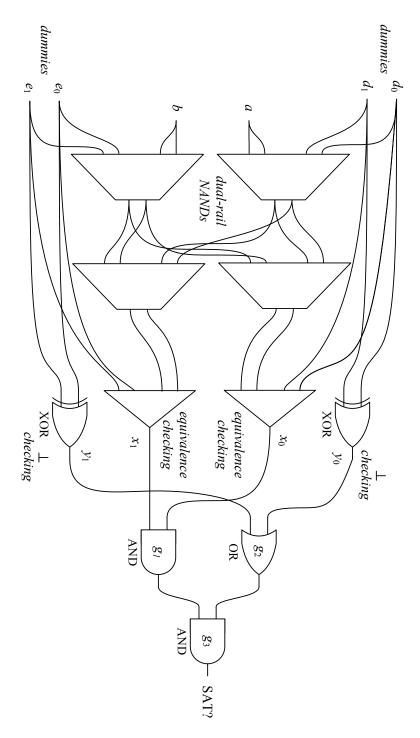

#### 2.1.3 SAT-Based Synthesis

This chapter tackles the problem of synthesizing cyclic combinational circuits with SAT-based techniques. Specifically, we build off of a technique based on Craig interpolation for synthesizing functional dependencies [23]. This technique is geared towards technologies where the complexity of implementing a function is heavily dependent on the number of support variables.

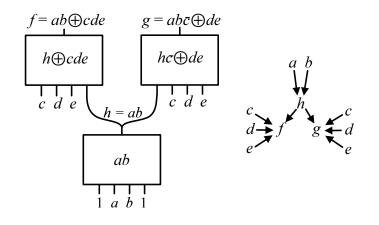

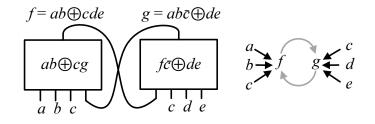

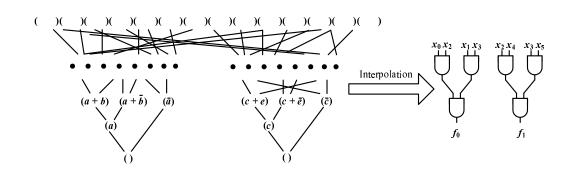

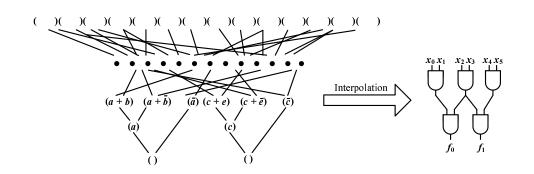

This is illustrated conceptually in Figure 2.5. The figure shows three functions: f(h, c, d, e), g(h, c, d, e), and h(a, b). Both f and g can be represented in terms of the support variables a, b, c, d, and e. However, if f and g are to be implemented in an acyclic topology in terms of four input look-up tables, at least one additional look-up table must be used (in this case h(a, b)).

Whether or not a function can be represented in terms of certain support variables can be cast as a SAT problem. If the answer is affirmative, Craig interpolation provides an implementation. Figure 2.6 demonstrates that an alternative representation exists for f, and g. Craig interpolation can be used to generate the functions f(a, b, c, g) and g(f, c, d, e), and a SAT solver can verify whether or not this representation behaves combinationally.

Figure 2.5: Three four-input lookup tables implement functions  $f = ab \oplus cde$  and  $g = ab\overline{c} \oplus de$  using an acyclic topology. The circuit's dependency graph is shown on the right.

Figure 2.6: Two four-input lookup tables implement functions  $f = ab \oplus cde$  and  $g = ab\overline{c} \oplus de$  using a cyclic topology. The circuit's dependency graph is shown on the right.

#### 2.2 Circuit and Network Model

Analysis of an acyclic circuit is transparent. We first evaluate the gates connected only to primary inputs, and then gates connected to these and primary inputs, and so on, until we have evaluated all gates. The previous values of the internal signals do not enter into play.

We adopt a *ternary framework* for analysis. We assume that, at the outset, all wires in a circuit have *undefined* values, which we denote with the symbol  $\perp$ . Here  $\perp$  captures both uncertainty as well as possible ambiguity: the signal might be 0 or 1 – but we do not know which; or it might not even have logical value, i.e., it could be a voltage value between logical 0 and logical 1. We say that a variable's value is *definite* or *known* if its value is 0 or 1 and that it is *indefinite* or *ambiguous* if it is  $\perp$ . The idea of three-valued logic for circuit analysis is well established. It was originally proposed for the analysis of *hazards* in combinational logic [24]. Bryant popularized its use for verification [25], and it has been widely adopted for the analysis of asynchronous circuits [26].

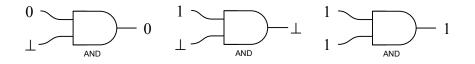

Conceptually, when validating a cyclic circuit, we apply definite values to the inputs, and track the propagation of signal values. Initially, each gate has an output value of  $\perp$ . We ask: is there sufficient information to conclude that the gate output is 0 or 1? If yes, we assign this value as the output; otherwise, the value  $\perp$  persists. For instance, with an AND gate, if the inputs include a 0, then the output is 0, regardless of other  $\perp$  inputs. If the inputs consist of 1 and  $\perp$  values, then the output is  $\perp$ . Only if all the inputs are 1 is the output 1. This is illustrated in Figure 2.7. Input values that determine the gate output are called *controlling*.

Figure 2.7: An AND gate with 0, 1, and  $\perp$  inputs.

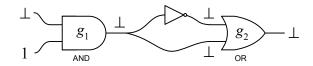

Consider the circuit fragment in Figure 2.8. One might be tempted to reason as follows: the output of the AND gate  $g_1$  is fed in complemented and uncomplemented form into the OR gate  $g_2$ . Thus, one of the inputs to the OR gate must be 1, and so its output must be 1. And yet, by definition,  $\perp$  designates an unknown, possibly undefined value. (For instance, in an actual circuit, it could indicate a voltage value exactly half way between logical 0 and logical 1.) In our analysis, we remain agnostic: the output of the OR gate is  $\perp^1$ .

Figure 2.8: An illustration unknown/undefined values  $\perp$ .

In the analysis, we track the propagation of well-defined signal values. Once a definite value is assigned to an internal wire, this value persists for the duration (so long as the input values are held constant). For any input assignment, a circuit reaches a so-called *fixed point* in the ternary framework: a state where no further updates of controlling values are possible. This fixed point is unique [26]. We adopt the following definition.

<sup>&</sup>lt;sup>1</sup> In standard CMOS technologies, it is possible for a gate to output a voltage value between the noise margin if its inputs are also somewhere between logical 0 and logical 1. Remaining agnostic about the value of  $g_2$  in Figure 2.8 allows us to invalidate circuits where this could be a concern

A circuit is *combinational* iff, for every assignment of input values, with all the wires initially set to  $\perp$ , the circuit reaches a fixed point that does not contain any  $\perp$  values.

We illustrate our circuit model with the following example.

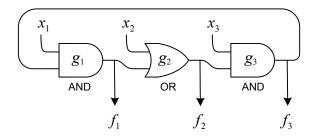

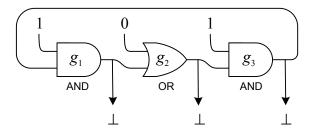

**Example 1** Consider the circuit shown in Figure 2.9, consisting of an AND gate  $g_1$ , an OR gate  $g_2$ , and an AND gate  $g_3$ , in a cycle. By inspection, note that if  $x_1 = 0$ then  $f_1$  assumes value 0; if  $x_2 = 1$  then  $f_2$  assumes value 1; and if  $x_3 = 0$  then  $f_3$ assumes value 0. But what happens if  $x_1 = 1$ ,  $x_2 = 0$  and  $x_3 = 1$ ? In this case, all the outputs equal  $\perp$ , as illustrated in Figure 2.10. The outcome for all eight cases is shown in Figure 2.11. We conclude that the circuit is not combinational.

#### 2.2.1 Gate Level vs. Functional Level Analysis

The algorithms and concepts presented in the begining of this chapter are applicable to technology-independent synthesis. At this level, a circuit is specified as a network that computes Boolean functions. Ultimately, such a network gets mapped to gates in a specific technology. The validity of a cyclic combinational circuit is properly established in terms of *controlling values* at the technology level. At the network level, we validate circuits in terms of *functional dependencies*. The notion of a function depending on a variable is similar but not identical to the concept of a Boolean value controlling the output of a gate. There can be subtle issues when mapping valid network level cyclic specifications to gate level specifications. This was first demonstrated in [27]

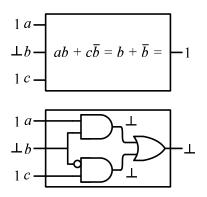

Figure 2.12 demonstrates an example of a function that may behave differently depending on its gate level mapping. Before the function  $f(a, b, c) = ab + c\bar{b}$  is mapped to gates,  $f(1, b, 1) = b + \bar{b} = 1$ . However, the axiom  $b + \bar{b} \equiv 1$  only holds if it is assumed that the values on the wires are truly Boolean (as demonstrated in Figure 2.8). In the case were  $b = \bot$ , it is possible that b is some value between 1 and 0, and in this

Figure 2.9: A cyclic circuit that is not combinational.

Figure 2.10: The circuit of Figure 2.9 with  $x_1 = 1$ ,  $x_2 = 0$  and  $x_3 = 1$ .

| $x_1$ | $x_2$ | $x_3$ | $f_1$ | $f_2$   | $f_3$   |

|-------|-------|-------|-------|---------|---------|

| 0     | 0     | 0     | 0     | 0       | 0       |

| 0     | 0     | 1     | 0     | 0       | 0       |

| 0     | 1     | 0     | 0     | 1       | 0       |

| 0     | 1     | 1     | 0     | 1       | 1       |

| 1     | 0     | 0     | 0     | 0       | 0       |

| 1     | 0     | 1     |       | $\perp$ | $\perp$ |

| 1     | 1     | 0     | 0     | 1       | 0       |

| 1     | 1     | 1     | 1     | 1       | 1       |

Figure 2.11: Analysis of the circuit in Figure 2.9.

case the mapped circuit shown in Figure 2.12 will evaluate to a different value than the unmapped function f(a, b, c).

An assignment of a subset of a function's support variables is said to be a *controlling assignment* if the function evaluates to the same value regardless of the assignment of the other variables in the function's support set. We sometimes say that a variable assignment *controls* a function, if that variable assignment is a controlling assignment for that function.

In the beginning of this chapter, analysis and synthesis is performed on the level of Boolean functions. We assume that a function evaluates to definite values for all controlling assignments to that function's support variables. Later, we explore methods of mapping and analyzing cyclic circuits at the level of gates. We prove that any set of cyclic functions that is deemed combinational can be mapped to a gate-level design. We provide a constructive method for performing the mapping.

Figure 2.12: The function  $ab + c\bar{b}$  and a gate level implementation.

## 2.3 Functional Dependencies

At the network level, a circuit is specified as a collection of nodes  $\mathcal{N}$ . Associated with each node is a node function  $f_i$  and a corresponding internal variable  $y_i$ ,  $0 \leq i \leq n-1$ . (We sometimes abuse the notation by using the same name for the function and the corresponding internal variable, calling them both  $f_i$ ). The node functions can depend on input variables as well as on other internal variables. In a network's dependency graph, a directed edge is drawn from node i to node j iff the node i is in the support set of node function  $f_j$ .

The process of multilevel logic synthesis typically consists of an iterative application of minimization, decomposition, and restructuring operations [28]. An important step at the technology-independent stage is the task of structuring *functional dependencies*. (With SOP representations, this step was called *substitution* or *resubstitution*.) In this step, node functions are expressed or re-expressed in terms of other node functions as well as the primary inputs.

For each node function, different choices might be available as dependencies yielding alternative expressions of varying cost. Throughout this chapter, we will focus on *support set size* as our cost metric. Given the focus on technology-independent synthesis algorithms, based on Boolean satisfiability, this metric is appropriate. (If we were using an SOP representation, we could use literal counts instead.) Consider the functions  $f_1$ and  $f_2$ ,

$$f_1 = bcx + bdx + ab \tag{2.2}$$

$$f_2 = abc\bar{x} + cx + d. \tag{2.3}$$

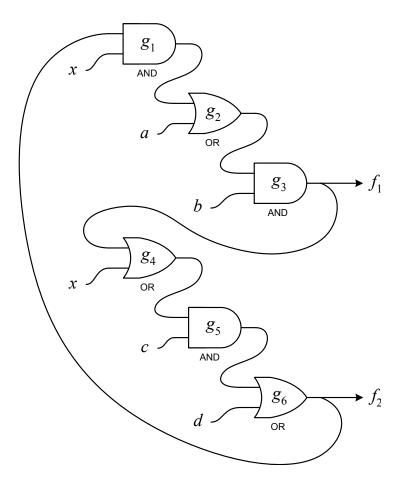

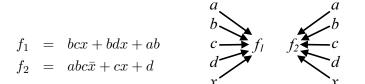

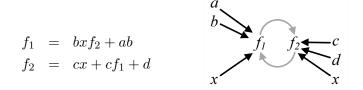

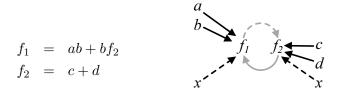

Figure 2.13 shows four different expressions for the functions and the corresponding dependency graphs. Figure 2.13.a shows expressions for  $f_1$  and  $f_2$ , both in terms of the primary input variables only. With a support set of  $\{a, b, c, d, x\}$ , the cost of both of these expressions is 5, so the total cost is 10.

Figures 2.13.b and 2.13.c show alternate expressions, obtained by introducing functional dependencies. In Figure 2.13.b,  $f_1$  is expressed in terms of  $f_2$  and  $\{a, b, x\}$ . Accordingly, the total cost is 9. In Figure 2.13.c,  $f_2$  is expressed in terms of  $f_1$  and  $\{c, d, x\}$ . Accordingly, the total cost is also 9.

In existing methodologies, a total ordering is enforced among the functions in this phase in order to ensure that no cycles occur. In this example, the ordering of  $f_2 \sqsubseteq f_1$ would produce the expressions in Figure 2.13.b; the ordering of  $f_1 \sqsubseteq f_2$  would produce the expressions in Figure 2.13.c. Insisting upon an ordering means that we would have to choose one of these two results.

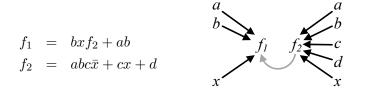

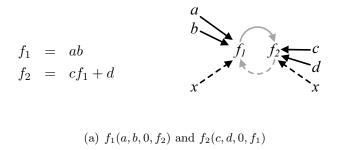

However, if we allow cyclic dependencies, we can find a better solution. Figure 2.13.d show expressions for  $f_1$  and  $f_2$  with support sets of  $\{a, b, x, f_2\}$  and  $\{c, d, x, f_1\}$ , so a total cost 8. As the dependency graph in Figure 2.13.d illustrates, the functional dependencies are cyclic. Yet for every assignment of the primary input variables a, b, c, d, and x, the functions evaluate to definite Boolean values. The functions and dependency graphs for functions  $f_1$  and  $f_2$  when x is 0 and x is 1 are shown in Figure 2.14. We see that, for any assignment of x, the cyclic dependency between  $f_1$  and  $f_2$  is broken, so the result is combinational.

Of course, not all choices of cyclic dependencies are valid. Many will result in networks that are not combinational. Suppose we wish to compute some complicated function f and its complement  $\bar{f}$ . Saying that

$$f = \bar{f},$$

$$\bar{f} = f,$$

is evidently meaningless.

(a)

$$f_1(a, b, c, d, x)$$

and  $f_2(a, b, c, d, x)$

(b)

$$f_1(a, b, x, f_2)$$

and  $f_2(a, b, c, d, x)$

$$f_1 = bcx + bdx + ab$$

$$f_2 = cx + cf_1 + d$$

$$a$$

$$b$$

$$c$$

$$d$$

$$f_1$$

$$f_2$$

$$c$$

$$d$$

$$x$$

(c)  $f_1(a, b, c, d, x)$  and  $f_2(c, d, x, f_1)$

(d)  $f_1(a, b, x, f_2)$  and  $f_2(c, d, x, f_1)$

Figure 2.13: Four different implementations of two functions,  $f_1$  and  $f_2$ , of five variables a, b, c, d, and x.

(b)  $f_1(a, b, 1, f_2)$  and  $f_2(c, d, 1, f_1)$

Figure 2.14: Functions  $f_1(a, b, x, f_2)$  and  $f_2(c, d, x, f_1)$  with x = 0 and x = 1. For both values of x, the dependency graphs become acyclic.

#### 2.3.1 Functional Dependencies with Craig Interpolation

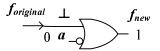

In a seminal paper, McMillan proposed a SAT-based method for symbolic model checking based on computing so called Craig interpolants [1]. In [23], the method was applied to the problem of synthesizing functional dependencies. Broadly, the strategy is to formulate an instance of Boolean satisfiability (SAT) that asks whether or not a target function can be implemented with a certain support set. A proof of unsatisfiability, returned by a SAT solver, is converted into a circuit that computes the target function. We give a brief review of the method here, noting that in its current form, it is only applicable to acyclic orderings. In the next section, we generalize the method to cyclic orderings.

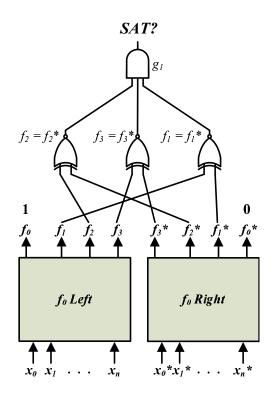

The method constructs a miter, as shown Figure 2.15. Here  $f_0$  is the target function. The satisfiability of the primary output of this circuit indicates whether or not there exists a dependency function  $h(f_1, f_2, f_3)$  that can be used to represent  $f_0$  for some network. Here  $f_0$  Left and  $f_0$  Right are two copies of the same network. The primary inputs  $x_0, x_1, \ldots, x_n$  (referred to as X) are the primary inputs to  $f_0$  Left. The primary inputs  $x_0^*, x_1^*, \ldots, x_n^*$  (referred to as  $X^*$ ) are the primary inputs to  $f_0$  Right; these are distinct sets of variables, but in direct correspondence with one another:  $f_i(X)$  is equivalent to  $f_i^*(X^*)$  where the assignment of X is equal to the assignment of  $X^*$ .

If the primary output of this circuit is satisfiable, then there exists a pair of input assignments X and X\* such that  $f_0(X) \neq f_0^*(X^*)$  and  $f_1(X) = f_1^*(X^*)$ ,  $f_2(X) = f_2^*(X^*)$ ,  $f_3(X) = f_3^*(X^*)$ . Thus the value of  $f_0$  cannot be determined solely from the values of  $f_1$ ,  $f_2$ , and  $f_3$ .

Then this indicates that  $f_0$  evaluates to a different value from  $f_0^*$  while functions  $f_1$ ,  $f_2$ , and  $f_3$  evaluate to the same values of  $f_1^*$ ,  $f_2^*$ ,  $f_3^*$ , respectively, on each side of the circuit for some assignment of X and X<sup>\*</sup>. Clearly this indicates that the ON set  $f_0(f_1, f_2, f_3)^1$  is not disjoint from the OFF set  $f_0(f_1, f_2, f_3)^0$ . Accordingly, there is no function  $h(f_1, f_2, f_3)$  that is equivalent to  $f_0(X)$  (or to  $f_0^*(X^*)$ ).